展望未来,时钟晶振技术将持续演进,以应对更高速、更集成、更智能和更严苛的应用需求。在性能维度,对亚皮秒级抖动、百GHz级频率、以及接近原子钟长期稳定性的追求将推动新材料(如氮化铝薄膜体声波谐振器)和新结构的发展。在集成维度,将时钟晶振与时钟发生器、网络同步器、甚至特定功能IP核(如SerDes)进行2.5D/3D先进封装的系统级时钟解决方案将更常见。在智能维度,支持实时状态监控、动态频率校准、软件配置及故障预测的健康管理型智能时钟晶振将增加系统韧性。同时,面对自动驾驶、6G、量子计算等前沿领域,时钟晶振需要在极端可靠性、低噪声和复杂环境适应性上实现新的突破。无论形态与技术如何变迁,时钟晶振作为数字世界同步与计时的物理基石这一根本角色不会改变,它将继续以好的性能支撑起日益庞大和智能的全球信息基础设施。时钟晶振是服务器主板的元件之一。龙岗区无源晶振时钟晶振售价

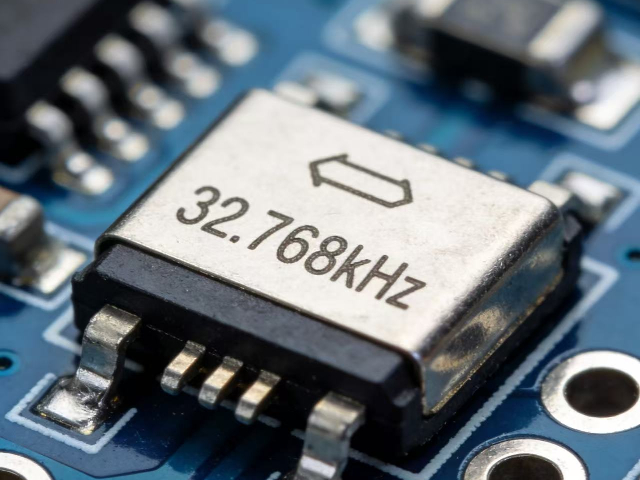

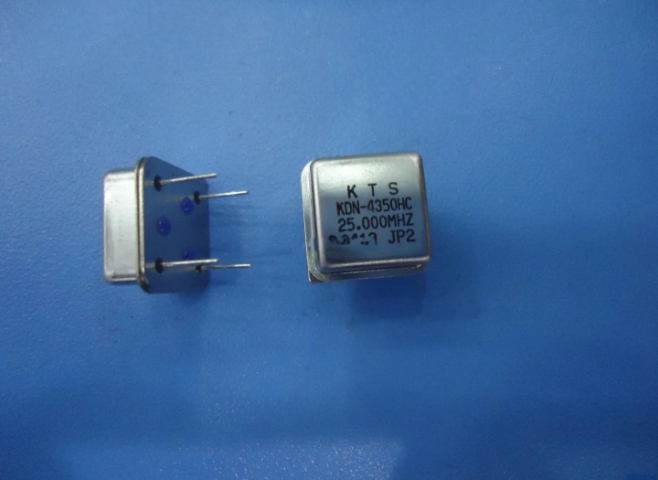

时钟晶振,作为数字电路的“心脏”与“节拍器”,其功能是为整个电子系统提供一个稳定、精确的基准时钟信号。与需要电压控制来调整频率的压控晶振(VCXO)或为实时时钟(RTC)芯片提供32.768kHz计时信号的RTC晶振不同,标准时钟晶振通常输出一个固定的、高精度的频率,如25MHz、50MHz等,直接驱动微处理器(MCU/MPU)、现场可编程门阵列(FPGA)、数字信号处理器(DSP)或用集成电路(ASIC)的时钟输入引脚。它的稳定性直接决定了芯片内部数十亿晶体管的开关时序,进而影响系统总线速度、数据处理速率乃至通信接口的同步精度。一颗高质量的时钟晶振,是确保数字系统高速、稳定、无错运行的基石。在数据中心服务器、网络通信设备、测试仪器等领域,时钟晶振的相位噪声和抖动性能尤为重要,微小的时序偏差都可能导致数据传输出错或测量失准。龙岗区无源晶振时钟晶振售价鑫和顺时钟晶振支持多种工作电压。

时钟晶振的相位噪声与时间抖动是衡量其频谱纯度和时序精度的关键指标,对高速数字与混合信号系统影响深远。相位噪声描述了理想时钟信号能量在频域上的扩散程度,表现为载波两侧的噪声边带;而时间抖动则是该噪声在时域上的直接体现,表现为时钟边沿相对于理想位置的随机偏移。在高速串行通信(如PCIe 6.0, USB4, 400G以太网)中,参考时钟的抖动会直接压缩数据眼图的水平张开度,提升误码率。在射频系统中,用于本振频率合成的参考时钟晶振,其相位噪声会直接转化为发射信号的带外杂散和接收机的底噪抬升,恶化系统信噪比与邻道选择性。因此,评估一颗时钟晶振时,必须详尽分析其在关键频偏点(如10Hz, 100Hz, 1kHz, 10kHz, 1MHz)的单边带相位噪声谱密度,以及在不同积分带宽(如12kHz-20MHz)下的随机抖动与确定性抖动。先进的设计通过采用超高Q值AT切晶体、低噪声有源电路、优化的电源滤波及恒温/温补技术,将时钟晶振的相位噪声与抖动控制在极低水平。

在专业音视频处理与传输设备中,时钟晶振负责为ADC/DAC、数字音频处理器、视频编解码器及显示接口提供主时钟。音频系统的音质对时钟抖动极为敏感,时钟抖动会通过数模转换过程直接引入非线性失真和本底噪声。因此,音频设备(如专业录音接口、数字调音台、Hi-Fi DAC)常采用低抖动的音频时钟晶振,其频率通常是音频采样率(如44.1kHz, 48kHz)的整数倍(如22.5792MHz, 24.576MHz)。在视频领域,像素时钟的稳定性与准确性决定了画面显示的同步性、刷新率精度和分辨率。例如,在HDMI 2.1发送器中,处理4K/8K高刷新率视频所需的时钟晶振必须具有极高的频率稳定性和极低的抖动,以确保无撕裂的高质量图像输出。多媒体应用对时钟的电磁兼容性设计也要求颇高,需防止时钟噪声干扰敏感的模拟信号通路。我们的时钟晶振提供CMOS输出电平。

在电磁兼容设计中,时钟晶振及其时钟线既是潜在的敏感电路,也是主要的干扰辐射源。作为敏感部分,时钟晶振易受附近开关电源、电机驱动器、大电流数字芯片产生的强电磁场干扰,导致输出信号出现周期抖动或杂散。因此,布局时应使其远离这些噪声源,并可为时钟晶振本身增加金属屏蔽罩。作为干扰源,时钟晶振输出的方波信号富含奇次谐波,这些高频能量可能通过时钟线(作为单极天线)或电源/地平面耦合辐射出去,导致设备电磁辐射超标。抑制辐射的措施包括:使用扩频时钟晶振(通过轻微调制时钟频率,将能量分散到更宽频带,降低峰值辐射)、在时钟晶振输出端使用铁氧体磁珠或小电阻串联阻尼、确保时钟线在完整地平面参考下走线、并尽量缩短走线长度。妥善的EMC设计是产品通过相关认证、稳定上市的必要条件。鑫和顺时钟晶振的售后服务完善。龙岗区音叉晶振时钟晶振工厂

时钟晶振的短期稳定度非常重要。龙岗区无源晶振时钟晶振售价

可编程时钟晶振(又称可编程振荡器)通过集成传统时钟晶振、小数/整数分频锁相环及配置存储器,提供了前所未有的灵活性。用户可以通过I2C、SPI或引脚配置,在极宽的频率范围(如1MHz至2.1GHz)内,动态生成数十个甚至上百个离散的高精度频率点,并可选多种输出电平和格式。这种器件极大地简化了多时钟域系统的设计,用一个硬件型号即可适应产品开发不同阶段的需求变更,或支持多模多频的通信设备(如软件定义无线电、多制式小基站)。尽管其相位噪声和抖动可能略逊于同等级别的固定频率时钟晶振,但其在减少物料种类、简化供应链、加速产品上市方面的优势非常明显,特别适合原型开发、中小批量及多配置产品。龙岗区无源晶振时钟晶振售价

深圳市鑫和顺科技有限公司汇集了大量的优秀人才,集企业奇思,创经济奇迹,一群有梦想有朝气的团队不断在前进的道路上开创新天地,绘画新蓝图,在广东省等地区的电子元器件中始终保持良好的信誉,信奉着“争取每一个客户不容易,失去每一个用户很简单”的理念,市场是企业的方向,质量是企业的生命,在公司有效方针的领导下,全体上下,团结一致,共同进退,**协力把各方面工作做得更好,努力开创工作的新局面,公司的新高度,未来深圳市鑫和顺科技供应和您一起奔向更美好的未来,即使现在有一点小小的成绩,也不足以骄傲,过去的种种都已成为昨日我们只有总结经验,才能继续上路,让我们一起点燃新的希望,放飞新的梦想!