FPGA定制项目之机器人视觉识别辅助模块开发某机器人企业需定制FPGA视觉识别辅助模块,搭配机器人完成物料分拣,要求识别5种物料,识别准确率不低于95%,响应时间小于300ms。项目团队选用LatticeECP5系列FPGA,其高速接口可对接200万像素工业相机。FPGA接收相机图像数据,实现图像预处理(降噪、边缘检测)与特征提取逻辑,通过匹配算法识别物料类型,再将结果传输至机器人控制器。开发中优化算法并行处理流程,提升识别速度。测试时在不同光照环境下验证,模块识别准确率达96.3%,响应时间280ms,助力机器人分拣效率提升15%。高清视频处理的 FPGA 定制,加速编解码,满足影视制作高要求。山东安路FPGA定制项目

FPGA定制项目之消费电子VR设备图像处理模块开发某电子厂商需定制FPGA图像处理模块,用于VR头显设备,要求实现双目图像实时拼接与畸变矫正,图像分辨率支持2K,帧速率保持90fps,避免用户产生眩晕感。项目团队选用LatticeCrossLink-NX系列FPGA,其低功耗与高速图像渲染能力适配VR设备便携需求。FPGA接收双路摄像头采集的图像数据,先通过畸变矫正算法修正镜头光学偏差,再采用图像融合技术完成双目图像拼接,同时根据用户头部运动数据调整图像视角,确保画面与头部动作同步。硬件设计简化电路结构,降低模块体积与重量,适配VR头显紧凑空间;软件层面优化算法运行流程,减少图像处理延迟。测试中,模块图像拼接偏差小于1像素,帧速率稳定在90fps,用户佩戴头显转动头部时,画面响应延迟小于10ms,有效降低眩晕感,符合VR设备沉浸式体验需求。 江西ZYNQFPGA定制项目机器人手臂控制的 FPGA 定制,实现高精度抓取与操作。

FPGA定制项目之医疗心电信号采集模块开发某医疗设备厂商需定制FPGA心电信号采集模块,用于便携式心电监测仪,要求采集3通道心电信号,采样率200Hz,噪声抑制比大于60dB。项目组选用符合医疗电子标准的FPGA芯片,搭配高精度ADC与导联接口。FPGA实现心电信号采集、放大与滤波逻辑,去除工频干扰与肌电干扰,再将处理后的数据传输至存储模块。硬件设计加入隔离电路,软件层面符合医疗数据安全规范。经第三方检测,模块采集信号失真度小于1%,噪声抑制比达65dB,可集成到监测仪中用于日常心电监测。

FPGA定制项目之消费电子智能手环睡眠监测模块开发某可穿戴设备厂商需定制FPGA智能手环睡眠监测模块,用于睡眠质量分析,要求监测睡眠时长、深睡/浅睡/REM睡眠阶段,监测误差小于15分钟,且功耗低于3mW。项目团队选用LatticeCrossLink-NX系列FPGA,其低功耗与生物信号处理能力适配手环需求。FPGA接收手环内置的加速度传感器与心率传感器数据,通过睡眠特征提取算法分析用户运动状态与心率变化,划分睡眠阶段,统计睡眠时长,生成睡眠报告。硬件设计简化电路,降低模块功耗;软件层面优化采样频率,睡眠时降低采样间隔。测试中,模块睡眠时长监测误差10分钟,睡眠阶段识别准确率达85%,连续监测7天消耗手环8%电量,满足用户睡眠质量监测需求。 气象监测的 FPGA 定制,提高气象参数测量精度与预报准确性。

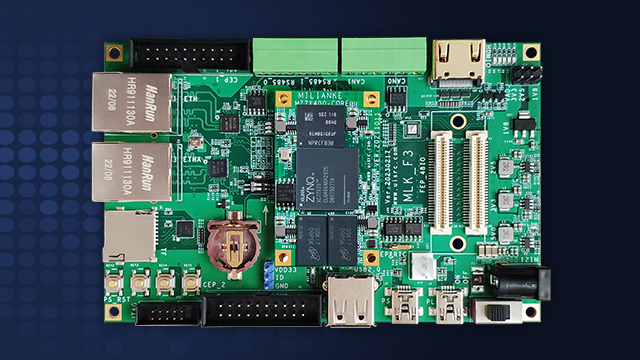

FPGA定制项目之智慧零售自动收银扫码识别模块开发某零售科技公司需定制FPGA自动收银扫码识别模块,用于无人收银台,要求识别商品一维码、二维码,识别距离5-20cm,识别时间小于秒,且支持多商品连续扫码。项目团队选用XilinxZynq-7000系列FPGA,其高速图像识别与并行处理能力适配收银效率需求。FPGA对接收银台高清扫描相机,接收商品条码图像后,通过图像预处理(去模糊、增强对比度)与条码解码算法提取商品信息,与后台数据库匹配获取价格,发送至收银系统完成结算。硬件设计加入补光模块,适配不同光线环境;软件层面支持条码快速连续识别,避免漏扫。测试中,模块识别距离覆盖5-22cm,识别时间秒,连续扫码准确率达,满足无人收银台高效结算需求。 设计 FPGA 的电机变频调速系统,灵活调整电机运行速度。山东安路FPGA定制项目

智能交通的 FPGA 定制,动态优化信号灯,缓解城市交通拥堵。山东安路FPGA定制项目

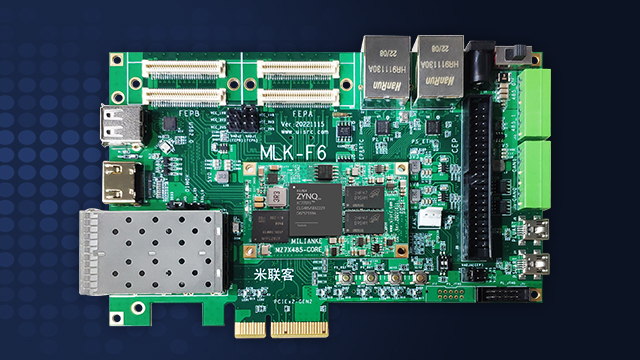

通信基站信号处理FPGA定制项目某5G通信基站信号处理模块定制项目中,需求是实现10Gbps以上的高速信号解调与滤波。项目团队采用自顶向下设计方法论,先完成系统架构规划,将信号处理流程拆解为同步、解调、均衡等子模块。硬件选型上选用XilinxZynqUltraScale+系列FPGA,其集成的硬核处理器可负责配置管理,可编程逻辑资源实现并行信号处理。开发阶段通过Vivado工具链进行RTL编码与综合优化,针对滤波器模块采用流水线设计,将关键路径延迟缩短至,满足300MHz时钟需求。测试阶段运用ModelSim构建复杂测试激励,结合ChipScope在线调试,解决了时钟域交叉导致的信号抖动问题,终实现误码率低于1e-9的性能指标,适配多频段基站部署场景。 山东安路FPGA定制项目