- 品牌

- 赛瑞达

- 型号

- sunred

- 基材

- 不锈钢

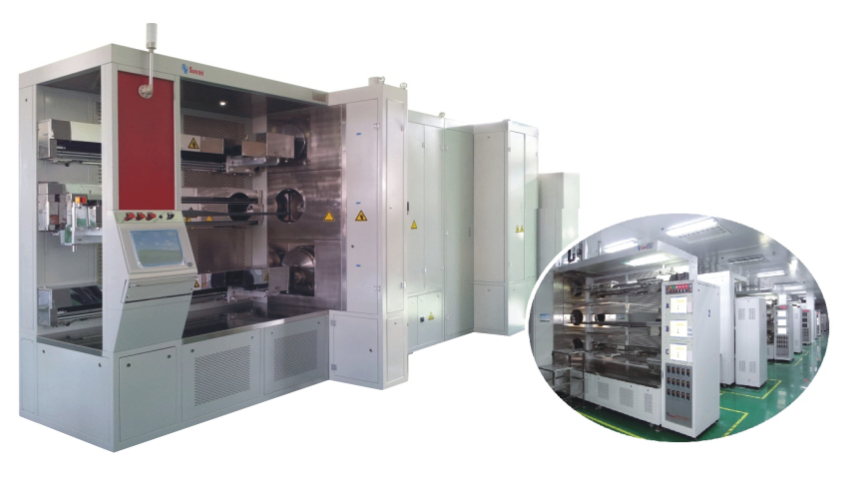

在半导体晶圆制造环节,管式炉的应用对提升晶圆质量与一致性意义重大。例如,在对 8 英寸及以下晶圆进行处理时,一些管式炉采用立式批处理设计,配合优化的气流均匀性设计与全自动压力补偿,从源头减少膜层剥落、晶格损伤等问题,提高了成品率。同时,关键部件寿命的提升以及智能诊断系统的应用,确保了设备的高可靠性及稳定性,为科研与生产提供有力保障。双温区管式炉在半导体领域展现出独特优势。其具备两个单独加热单元,可分别控制炉体两个温区,不仅能实现同一炉体内不同温度区域的稳定控制,还可根据实验或生产需求设置温度梯度,模拟复杂热处理过程。在半导体晶圆的退火处理中,双温区设计有助于优化退火工艺,进一步提高晶体质量,为半导体工艺创新提供了更多可能性。管式炉配备智能控制系统,操作简便,提升生产效率,立即体验!珠三角国产管式炉合金炉

在太阳能电池的关键工艺 —— 掺杂工艺中,管式炉能够提供精确的高温环境,使杂质原子均匀地扩散到硅片内部,形成 P - N 结,这对于太阳能电池的光电转换效率起着决定性作用。此外,在制备太阳能电池的减反射膜和钝化层等关键薄膜材料时,管式炉可通过化学气相沉积等技术,精确控制薄膜的生长过程,确保薄膜的质量和性能,有效减少光的反射损失,提高太阳能电池的光电转换效率。随着对清洁能源需求的不断增加,半导体太阳能电池产业发展迅速,管式炉在其中的应用也将不断拓展和深化,为提高太阳能电池的性能和降低生产成本提供持续的技术支持。广东制造管式炉真空合金炉多种规格可选,满足不同半导体工艺需求,欢迎联系获取定制方案!

管式炉在硅外延生长中通过化学气相沉积(CVD)实现单晶层的可控生长,典型工艺参数为温度1100℃-1200℃、压力100-500Torr,硅源气体(SiH₄或SiCl₄)流量50-500sccm。外延层的晶体质量受衬底预处理、气体纯度和温度梯度影响明显。例如,在碳化硅(SiC)外延中,需在800℃下用氢气刻蚀去除衬底表面缺陷,随后在1500℃通入丙烷(C₃H₈)和硅烷(SiH₄)实现同质外延,生长速率控制在1-3μm/h以减少位错密度5。对于化合物半导体如氮化镓(GaN),管式炉需在高温(1000℃-1100℃)和氨气(NH₃)气氛下进行异质外延。通过调节NH₃与三甲基镓(TMGa)的流量比(100:1至500:1),可精确控制GaN层的掺杂类型(n型或p型)和载流子浓度(10¹⁶-10¹⁹cm⁻³)。此外,采用梯度降温(5℃/min)可缓解外延层与衬底间的热应力,降低裂纹风险。

管式炉精确控制的氧化层厚度和质量,直接影响到蚀刻过程中掩蔽的效果。如果氧化层厚度不均匀或存在缺陷,可能会导致蚀刻过程中出现过刻蚀或蚀刻不足的情况,影响电路结构的精确性。同样,扩散工艺形成的 P - N 结等结构,也需要在蚀刻过程中进行精确的保护和塑造。管式炉对扩散工艺参数的精确控制,确保了在蚀刻时能够准确地去除不需要的材料,形成符合设计要求的精确电路结构。而且,由于管式炉能够保证工艺的稳定性和一致性,使得每一片硅片在进入蚀刻工艺时都具有相似的初始条件,从而提高了蚀刻工艺的可重复性和产品的良品率,为半导体器件的大规模生产提供了有力支持。赛瑞达管式炉节能设计,契合半导体绿色发展,期待携手!

在半导体CVD工艺中,管式炉通过热分解或化学反应在衬底表面沉积薄膜。例如,生长二氧化硅(SiO₂)绝缘层时,炉内通入硅烷(SiH₄)和氧气,在900°C下反应生成均匀薄膜。管式炉的线性温度梯度设计可优化气体流动,减少湍流导致的膜厚不均。此外,通过调节气体流量比(如TEOS/O₂),可控制薄膜的介电常数和应力。行业趋势显示,低压CVD(LPCVD)管式炉正逐步兼容更大尺寸晶圆(8英寸至12英寸),并集成原位监测模块(如激光干涉仪)以提升良率。

适用于半导体研发与生产,助力技术创新,欢迎联系获取支持!珠三角国产管式炉合金炉

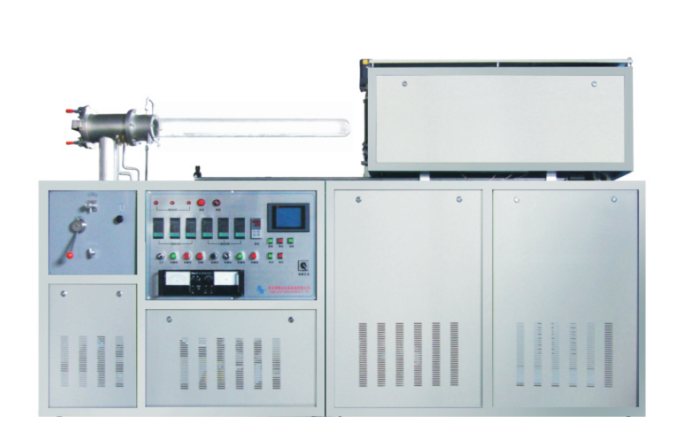

管式炉在半导体制造流程中占据着基础且关键的位置。其基本构造包括耐高温的炉管,多由石英或刚玉等材料制成,能承受高温且化学性质稳定,为内部反应提供可靠空间。外部配备精确的加热系统,可实现对炉内温度的精确调控。在半导体工艺里,管式炉常用于各类热处理环节,像氧化、扩散、退火等工艺,这些工艺对半导体材料的性能塑造起着决定性作用,从根本上影响着半导体器件的质量与性能。热氧化工艺是管式炉在半导体领域的重要应用之一。在高温环境下,通常是 800 - 1200°C,硅晶圆被放置于管式炉内,在含氧气氛中,硅晶圆表面会生长出二氧化硅(SiO₂)层。该氧化层用途范围广,例如作为栅极氧化层,这是晶体管开关的关键部位,其质量直接决定了器件性能与可靠性。干氧法生成的氧化层质量高,但生长速度较慢;湿氧法生长速度快,不过质量相对稍逊,而管式炉能够精确控制这两种方法所需的温度与气氛条件。珠三角国产管式炉合金炉

- 长沙8英寸管式炉化学气相沉积CVD设备TEOS工艺 2026-02-13

- 上海一体化管式炉真空合金炉 2026-02-13

- 北方制造管式炉低压化学气相沉积系统 2026-02-13

- 广州赛瑞达管式炉三氯氧磷扩散炉 2026-02-12

- 长三角国产管式炉生产厂家 2026-02-12

- 无锡一体化管式炉真空退火炉 2026-02-12

- 北方6吋管式炉真空合金炉 2026-02-11

- 北京6英寸管式炉化学气相沉积 2026-02-11

- 青岛8吋管式炉厂家供应 2026-02-11

- 中国电科赛瑞达管式炉合金炉 2026-02-10

- 长三角国产管式炉 2026-02-10

- 长三角第三代半导体管式炉三氯氧磷扩散炉 2026-02-10