- 品牌

- 士兰微,上海贝岭,新洁能,必易微

- 型号

- 10

- 制式

- 圆插头,扁插头

MOSFET的动态特性测试聚焦于开关过程中的参数变化,直接关系到高频应用中的开关损耗与电磁兼容性(EMC)。动态特性测试主要包括上升时间tr、下降时间tf、开通延迟td(on)与关断延迟td(off)的测量,需使用示波器与脉冲发生器搭建测试电路:脉冲发生器提供栅极驱动信号,示波器同步测量Vgs、Vds与Id的波形。

上升时间tr是指Id从10%上升到90%的时间,下降时间tf是Id从90%下降到10%的时间,二者之和决定了开关速度(通常为几十至几百纳秒),速度越慢,开关损耗越大。开通延迟是指从驱动信号上升到10%到Id上升到10%的时间,关断延迟是驱动信号下降到90%到Id下降到90%的时间,延迟过大会影响电路的时序控制。此外,动态测试还需评估米勒平台(Vds下降过程中的平台期)的长度,米勒平台越长,栅极电荷Qg越大,驱动损耗越高。在高频应用中,需选择tr、tf小且Qg低的MOSFET,减少动态损耗。 华微电子 MOSFET 适配电机驱动场景,与瑞阳微方案协同提升性能。标准MOS如何收费

MOS 的广泛应用离不开 CMOS(互补金属 - 氧化物 - 半导体)技术的支撑,两者协同构成了现代数字集成电路的基础。CMOS 技术的重心是将 NMOS 与 PMOS 成对组合,形成逻辑门电路(如与非门、或非门),利用两种器件的互补特性实现低功耗逻辑运算:当 NMOS 导通时 PMOS 关断,反之亦然,整个逻辑操作过程中几乎无静态电流,只在开关瞬间产生动态功耗。这种结构不仅大幅降低了集成电路的功耗,还提升了抗干扰能力与逻辑稳定性,成为手机芯片、电脑 CPU、FPGA、MCU 等数字芯片的主流制造工艺。例如,一个基本的 CMOS 反相器由一只 NMOS 和一只 PMOS 组成,输入高电平时 NMOS 导通、PMOS 关断,输出低电平;输入低电平时则相反,实现信号反相。CMOS 技术与 MOS 器件的结合,支撑了集成电路集成度的指数级增长(摩尔定律),从早期的数千个晶体管到如今的数百亿个晶体管,推动了电子设备的微型化、高性能化与低功耗化,是信息时代发展的重心技术基石。标准MOS如何收费瑞阳微提供全系列 MOSFET 选型服务,满足不同客户个性化技术要求。

MOSFET(金属-氧化物-半导体场效应晶体管)是一种基于电场效应控制电流的半导体器件,其主要点结构由源极(S)、漏极(D)、栅极(G)及衬底(B)四部分组成,栅极与沟道之间通过一层极薄的氧化层(通常为SiO₂)隔离,形成电容结构。这种绝缘栅设计使得栅极电流极小(近乎零),输入阻抗极高,这是其区别于BJT(双极结型晶体管)的关键特性。在N沟道增强型MOSFET中,当栅极施加正向电压且超过阈值电压Vth时,氧化层下的P型衬底表面会形成反型层(N型沟道),此时源漏之间施加正向电压即可产生漏极电流Id;而P沟道类型则需施加负向栅压,形成P型沟道。这种电压控制电流的机制,使其在低功耗、高频应用场景中具备天然优势,成为现代电子电路的主要点器件之一。

MOS管工作原理:电压控制的「电子阀门」MOS管(金属-氧化物-半导体场效应晶体管)的**是通过栅极电压控制导电沟道的形成,实现电流的开关或调节,其工作原理可拆解为以下关键环节:一、基础结构:以N沟道增强型为例材料:P型硅衬底(B)上制作两个高掺杂N型区(源极S、漏极D),表面覆盖二氧化硅(SiO₂)绝缘层,顶部为金属栅极G。初始状态:栅压VGS=0时,S/D间为两个背靠背PN结,无导电沟道,ID=0(截止态)。

二、导通原理:栅压诱导导电沟道栅压作用:当VGS>0(N沟道),栅极正电压在SiO₂层产生电场,排斥P衬底表面的空穴,吸引电子聚集,形成N型导电沟道(反型层)。沟道形成的临界电压称开启电压VT(通常2-4V),VGS越大,沟道越宽,导通电阻Rds(on)越小(如1mΩ级)。漏极电流控制:沟道形成后,漏源电压VDS使电子从S流向D,形成电流ID。线性区(VDS<VGS-VT):ID随VDS线性增加,沟道均匀导通;饱和区(VDS≥VGS-VT):漏极附近沟道夹断,ID*由VGS决定,进入恒流状态。 瑞阳微 MOSFET 技术支持及时,为客户解决应用中的各类技术难题。

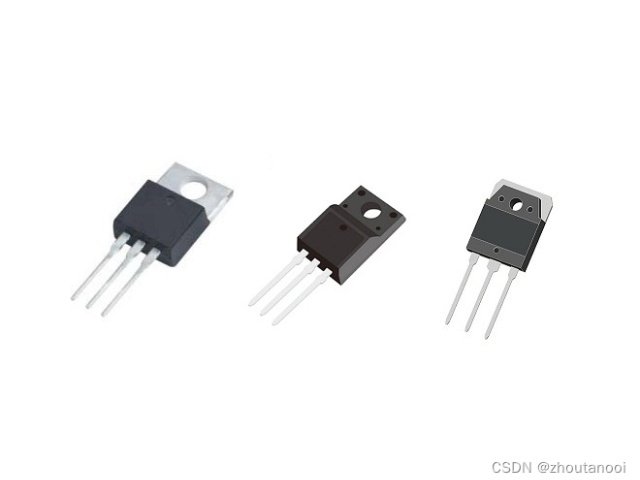

MOS 的分类维度丰富,不同类型的器件在性能与应用场景上形成明确区隔。按导电沟道类型可分为 N 沟道 MOS(NMOS)与 P 沟道 MOS(PMOS):NMOS 导通电阻小、开关速度快,能承载更大电流,是电源转换、功率控制的主流选择;PMOS 阈值电压为负值,驱动电路更简单,常用于低压逻辑电路或与 NMOS 组成互补结构。按导通机制可分为增强型(E-MOS)与耗尽型(D-MOS):增强型需栅极电压启动沟道,适配绝大多数开关场景;耗尽型零栅压即可导通,多用于高频放大、恒流源等特殊场景。按结构形态可分为平面型 MOS、沟槽型 MOS(Trench-MOS)与鳍式 MOS(FinFET):平面型工艺成熟、成本低,适用于低压小功率场景;沟槽型通过垂直沟道设计提升电流密度,适配中的功率电源;FinFET 通过 3D 栅极结构解决短沟道效应,是 7nm 以下先进制程芯片的重心元件。士兰微 SVF12N65F MOSFET 电流输出能力强,适配大功率驱动场景。通用MOS代理商

瑞阳微 RS3407 MOSFET 静态功耗低,适合电池供电设备长期使用。标准MOS如何收费

MOS管工作原理:电压控制的「电子阀门」导通原理:栅压诱导导电沟道栅压作用:当VGS>0(N沟道),栅极正电压在SiO₂层产生电场,排斥P衬底表面的空穴,吸引电子聚集,形成N型导电沟道(反型层)。沟道形成的临界电压称开启电压VT(通常2-4V),VGS越大,沟道越宽,导通电阻Rds(on)越小(如1mΩ级)。漏极电流控制:沟道形成后,漏源电压VDS使电子从S流向D,形成电流ID。线性区(VDS<VGS-VT):ID随VDS线性增加,沟道均匀导通;饱和区(VDS≥VGS-VT):漏极附近沟道夹断,ID*由VGS决定,进入恒流状态。标准MOS如何收费

MOSFET的动态特性测试聚焦于开关过程中的参数变化,直接关系到高频应用中的开关损耗与电磁兼容性(EMC)。动态特性测试主要包括上升时间tr、下降时间tf、开通延迟td(on)与关断延迟td(off)的测量,需使用示波器与脉冲发生器搭建测试电路:脉冲发生器提供栅极驱动信号,示波器同步测量Vgs、Vds与Id的波形。 上升时间tr是指Id从10%上升到90%的时间,下降时间tf是Id从90%下降到10%的时间,二者之和决定了开关速度(通常为几十至几百纳秒),速度越慢,开关损耗越大。开通延迟是指从驱动信号上升到10%到Id上升到10%的时间,关断延迟是驱动信号下降到90%到Id下降到90...

- 优势MOS代理商 2026-05-07

- 优势MOS成本价 2026-03-23

- 使用MOS 2026-03-23

- IGBTMOS收费 2026-03-22

- 高科技MOS如何收费 2026-03-22

- 什么是MOS销售方法 2026-03-22

- 使用MOS代理品牌 2026-03-22

- 威力MOS现价 2026-03-21

- 标准MOS一体化 2026-03-21

- 哪里有MOS使用方法 2026-03-20

- 现代化MOS价格合理 2026-03-19

- 进口MOS平均价格 2026-03-18

- 定制MOS成本价 2026-03-18

- 高科技MOS厂家现货 2026-03-18

- 哪些是MOS供应 2026-03-18

- 常规MOS销售厂 2026-03-17

- 贸易IGBT价格信息 04-05

- 优势IGBT哪里买 04-05

- 什么是IGBT资费 04-05

- 贸易IGBT模板规格 04-05

- IGBT厂家报价 04-04

- 哪里有IGBT批发价格 04-04

- 大规模IGBT厂家供应 04-04

- IGBT价格比较 04-04

- 什么是IGBT价格对比 04-04

- 大规模IGBT哪里买 04-03