- 品牌

- 京晓设计

- 服务内容

- 技术开发

- 版本类型

- 普通版

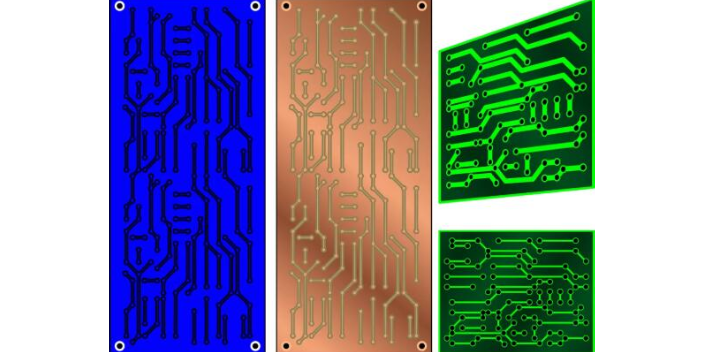

评估平面层数,电源平面数的评估:分析单板电源总数与分布情况,优先关注分布范围大,及电流大于1A以上的电源(如:+5V,+3.3V此类整板电源、FPGA/DSP的核电源、DDR电源等)。通常情况下:如果板内无BGA封装的芯片,一般可以用一个电源层处理所有的电源;如果有BGA封装的芯片,主要以BGA封装芯片为评估对象,如果BGA内的电源种类数≤3种,用一个电源平面,如果>3种,则使用2个电源平面,如果>6则使用3个电源平面,以此类推。备注:1、对于电流<1A的电源可以采用走线层铺铜的方式处理。2、对于电流较大且分布较集中或者空间充足的情况下采用信号层铺铜的方式处理。地平面层数的评估:在确定了走线层数和电源层数的基础上,满足以下叠层原则:1、叠层对称性2、阻抗连续性3、主元件面相邻层为地层4、电源和地平面紧耦合(3)层叠评估:结合评估出的走线层数和平面层数,高速线优先靠近地层的原则,进行层叠排布。屏蔽腔的设计具体步骤流程。湖北高速PCB设计规范

丝印调整,子流程:设置字符格式→调整器件字符→添加特殊字符→添加特殊丝印。设置字符格式,字符的宽度/高度:1/3盎司、1/2盎司(基铜):4/23Mil(推荐设计成4/25Mil);1盎司(基铜):5/30Mil;2盎司(基铜):6/45Mil;字高与字符线宽之比≥6:1。调整器件字符(1)字符与阻焊的间距≥6Mil。字符之间的距离≥6Mil,距离板边≥10Mil;任何字符不能重叠且不能被元器件覆盖。(2)丝印字符阴字线宽≥8mil;(3)字符只能有两个方向,排列应遵循正视时位号的字母数字排序为从左到右,从下到上。(4)字符的位号要与器件一一对应,不能颠倒、变换顺序,每个元器件上必须标出位号不可缺失,对于高密度板,可将位号标在PCB其他有空间的位置,用箭头加图框表示或者字符加图框表示,如下图所示。字符摆放完成后,逐个高亮器件,确认位号高亮顺序和器件高亮顺序一致。荆州定制PCB设计PCB设计工艺上的注意事项是什么?

结构绘制结构绘制子流程如下:绘制单板板框→绘制结构特殊区域及拼板→放置固定结构件。1.1.1绘制单板板框(1)将结构图直接导入PCB文件且测量尺寸,确认结构图形中结构尺寸单位为mm,显示比例为1:1等大。(2)设计文件中,单位为mm,则精度为小数点后4位;单位为Mil,则精度为小数点后2位,两种单位之间转换至多一次,特殊要求记录到《项目设计沟通记录》中。(3)导入结构图形并命名。(4)导入的结构图形层命名方式为DXF_日期+版本,举例:DXF_1031A1,线宽为0Mil。(5)结构图形导入后应在EDA设计软件视界正中,若偏移在一角,应整体移动结构图形,使之位于正中。(6)根据结构图形,绘制外形板框,板框与结构文件完全一致且重合,并体现在EDA设计软件显示层。(7)确定坐标原点,坐标原点默认为单板左边与下边延长线的交点,坐标原点有特殊要求的记录到《项目设计沟通记录》中。(8)对板边的直角进行倒角处理,倒角形状、大小依据结构图绘制,如无特殊要求,默认倒圆角半径为1.5mm,工艺边外沿默认倒圆角,半径为1.5mm并记录到《项目设计沟通记录》邮件通知客户确认。(9)板框绘制完毕,赋予其不可移动,不可编辑属性。

ADC/DAC电路:(2)模拟地与数字地处理:大多数ADC、DAC往往依据数据手册和提供的参考设计进行地分割处理,通常情况是将PCB地层分为模拟地AGND和数字地DGND,然后将二者单点连接,(3)模拟电源和数字电源当电源入口只有统一的数字地和数字电源时,在电源入口处通过将数字地加磁珠或电感,将数字地拆分成成模拟地;同样在电源入口处将数字电源通过磁珠或电感拆分成模拟电源。负载端所有的数字电源都通过入口处数字电源生成、模拟电源都通过经过磁珠或电感隔离后的模拟电源生成。如果在电源入口处(外部提供的电源)既有模拟地又有数字地、既有模拟电源又有数字电源,板子上所有的数字电源都用入口处的数字电源生成、模拟电源都用入口处的模拟电源生成。ADC和DAC器件的模拟电源一般采用LDO进行供电,因为其电流小、纹波小,而DC/DC会引入较大开关电源噪声,严重影响ADC/DAC器件性能,因此,模拟电路应该采用LDO进行供电。如何创建PCB文件、设置库路径?

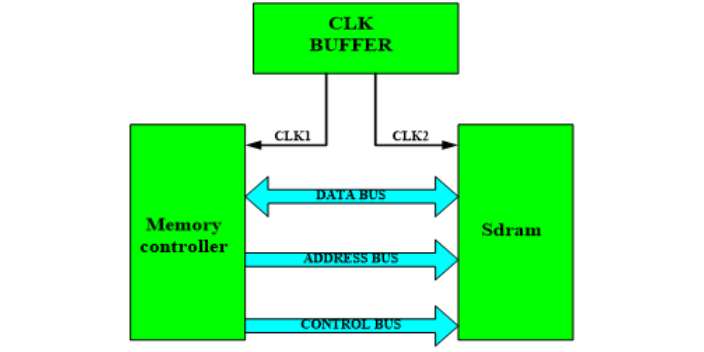

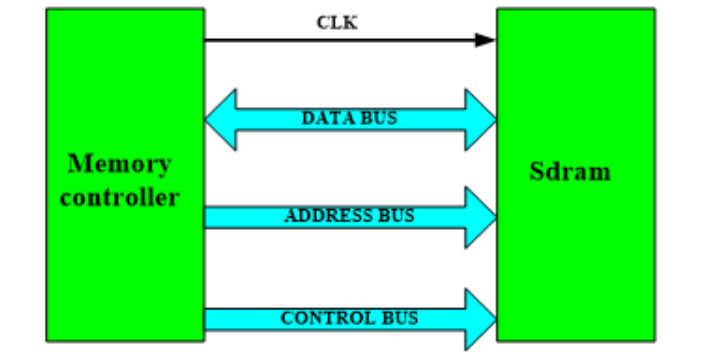

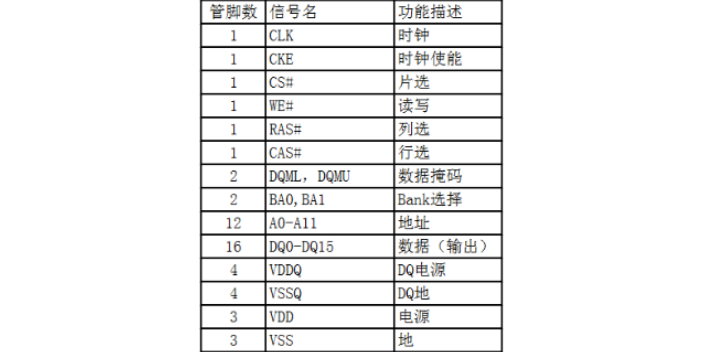

射频、中频电路(1)射频电路★基本概念1、射频:是电磁波按应用划分的定义,专指具有一定波长可用于无线电通信的电磁波,射频PCB可以定义为具有频率在30MHz至6GHz范围模拟信号的PCB。2、微带线:是一种传输线类型。由平行而不相交的带状导体和接地平面构成。微带线的结构如下图中的图1所示它是由导体条带(在基片的一边)和接地板(在基片的另一边)所构成的传输线。微带线是由介质基片,接地平板和导体条带三部分组成。在微带线中,电磁能量主要是集中在介质基片中传播的,3、屏蔽罩:是无线设备中普遍采用的屏蔽措施。其工作原理如下:当在电磁发射源和需要保护的电路之间插入一高导电性金属时,该金属会反射和吸收部分辐射电场,反射与吸收的量取决于多种不同的因素,这些因素包括辐射的频率,波长,金属本身的导电率和渗透性,以及该金属与发射源的距离。4、模块分腔的必要性:腔体内腔器件间或RF信号布线间的典型隔离度约在50-70dB,对某些敏感电路,有强烈辐射源的电路模块都要采取屏蔽或隔离措施,例如:a.接收电路前端、VCO电路的电源、环路滤波电路是敏感电路。b.发射的后级电路、功放的电路、数字信号处理电路、参考时钟和晶体振荡器是强烈的辐射源。SDRAM 的PCB布局布线要求是什么?鄂州了解PCB设计销售

PCB设计工艺的规则和技巧。湖北高速PCB设计规范

存储模块介绍:存储器分类在我们的设计用到的存储器有SRAM、DRAM、EEPROM、Flash等,其中DDR系列用的是多的,其DDR-DDR4的详细参数如下:DDR采用TSSOP封装技术,而DDR2和DDR3内存均采用FBGA封装技术。TSSOP封装的外形尺寸较大,呈长方形,其优点是成本低、工艺要求不高,缺点是传导效果差,容易受干扰,散热不理想,而FBGA内存颗粒精致小巧,体积大约只有DDR内存颗粒的三分之一,有效地缩短信号传输距离,在抗干扰、散热等方面更有优势,而DDR4采用3DS(3-DimensionalStack)三维堆叠技术来增大单颗芯片容量,封装外形则与DDR2、DDR3差别不大。制造工艺不断提高,从DDR到DDR2再到DDR3内存,其制造工艺都在不断改善,更高工艺水平会使内存电气性能更好,成本更低;DDR内存颗粒大范围采用0.13微米制造工艺,而DDR2采用了0.09微米制造工艺,DDR3则采用了全新65nm制造工艺,而DDR4使用20nm以下的工艺来制造,从DDR~DDR4的具体参数如下表所示。湖北高速PCB设计规范

武汉京晓科技有限公司是一家集生产科研、加工、销售为一体的****,公司成立于2020-06-17,位于洪山区和平乡徐东路7号湖北华天大酒店第7层1房26室。公司诚实守信,真诚为客户提供服务。公司现在主要提供**PCB设计与制造,高速PCB设计,企业级PCB定制等业务,从业人员均有**PCB设计与制造,高速PCB设计,企业级PCB定制行内多年经验。公司员工技术娴熟、责任心强。公司秉承客户是上帝的原则,急客户所急,想客户所想,热情服务。公司秉承以人为本,科技创新,市场先导,和谐共赢的理念,建立一支由**PCB设计与制造,高速PCB设计,企业级PCB定制**组成的顾问团队,由经验丰富的技术人员组成的研发和应用团队。京晓电路/京晓教育秉承着诚信服务、产品求新的经营原则,对于员工素质有严格的把控和要求,为**PCB设计与制造,高速PCB设计,企业级PCB定制行业用户提供完善的售前和售后服务。

仿真预分析:使用SI/PI仿真工具(如HyperLynx)验证信号反射、串扰及电源纹波。示例:DDR4时钟信号需通过眼图仿真确保时序裕量≥20%。3. PCB布局:从功能分区到热设计模块化布局原则:数字-模拟隔离:将MCU、FPGA等数字电路与ADC、传感器等模拟电路分区,间距≥3mm。电源模块集中化:将DC-DC转换器、LDO等电源器件放置于板边,便于散热与EMI屏蔽。热设计优化:对功率器件(如MOSFET、功率电感)采用铜箔散热层,热敏元件(如电解电容)远离发热源。示例:在LED驱动板中,将驱动IC与LED阵列通过热通孔(Via-in-Pad)连接至底层铜箔,热阻降低40%。信号流向: 尽...

- 恩施了解PCB设计 2025-11-26

- 黄冈设计PCB设计厂家 2025-11-26

- 恩施定制PCB设计规范 2025-11-26

- 鄂州打造PCB设计怎么样 2025-11-26

- 咸宁设计PCB设计销售电话 2025-11-26

- 武汉哪里的PCB设计功能 2025-11-26

- 恩施专业PCB设计教程 2025-11-26

- 哪里的PCB设计布线 2025-11-21

- 荆州常规PCB设计原理 2025-11-21

- 襄阳高速PCB设计哪家好 2025-11-21

- 黄石正规PCB设计功能 2025-11-21

- 鄂州高速PCB设计 2025-11-13

- 宜昌什么是PCB设计包括哪些 2025-11-13

- 咸宁专业PCB设计报价 2025-11-13

- 武汉高效PCB设计厂家 2025-11-13

- 宜昌常规PCB设计 2025-11-13

- 荆州印制PCB制板厂家 12-06

- 咸宁印制PCB制板多少钱 12-06

- 湖北打造PCB制板布线 12-06

- 湖北生产PCB制板厂家 12-06

- 宜昌印制PCB制板功能 12-06

- 孝感了解PCB制板包括哪些 12-06

- 武汉高速PCB制板原理 12-06

- 孝感高速PCB制板哪家好 12-05

- 孝感高速PCB制版加工 12-05

- 随州PCB制板厂家 12-05