- 品牌

- 京晓设计

- 服务内容

- 技术开发

- 版本类型

- 普通版

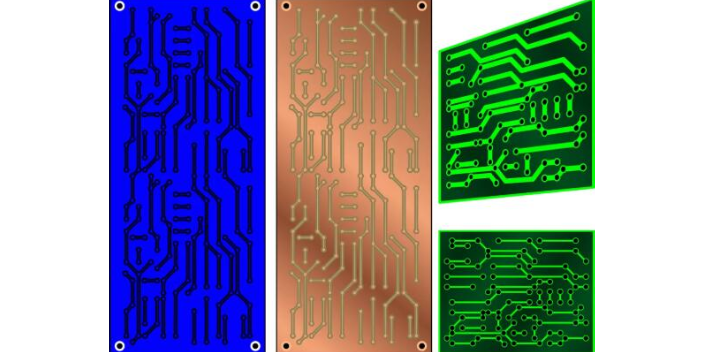

易发生这样有利于排除铜箔与基板间粘合剂受热产生的挥发性气体。一、每一块PCB上都必须用箭头标出过锡炉的方向:二、布局时,DIP封装的IC摆放的方向必须与过锡炉的方向成垂直,不可平行,如下图;如果布局上有困难,可允许水平放置IC(SOP封装的IC摆放方向与DIP相反)。三、布线方向为水平或垂直,由垂直转入水平要走45度进入。四、若铜箔入圆焊盘的宽度较圆焊盘的直径小时,则需加泪滴。如下图五、布线尽可能短,特别注意时钟线、低电平信号线及所有高频回路布线要更短。六、模拟电路及数字电路的地线及供电系统要完全分开。七、如果印制板上有大面积地线和电源线区(面积超过500平方毫米),应局部开窗口。如下图:八、横插元件(电阻、二极管等)脚间中心,相距必须湿300mil,400mil及500mil。(如非必要,240mil亦可利用,但使用与IN4148型之二极管或1/16W电阻上。1/4W电阻由)跳线脚间中心相距必须湿200mil,300mil,500mil,600mil,700mil,800mil,900mil,1000mil。九、PCB板上的散热孔,直径不可大于140mil。十、PCB上如果有Φ12或方形12MM以上的孔,必须做一个防止焊锡流出的孔盖,如下图(孔隙为)十一在用贴片元件的PCB板上,为了提高贴片元件的贴装准确性。 厚板材提供更好的机械支撑和抗弯曲能力。黄冈什么是PCB设计销售

注意高速信号的阻抗匹配,走线层及其回流电流路径(returncurrentpath),以减少高频的反射与辐射。在各器件的电源管脚放置足够与适当的去耦合电容以缓和电源层和地层上的噪声。特别注意电容的频率响应与温度的特性是否符合设计所需。对外的连接器附近的地可与地层做适当分割,并将连接器的地就近接到chassisground。可适当运用groundguard/shunttraces在一些特别高速的信号旁。但要注意guard/shunttraces对走线特性阻抗的影响。电源层比地层内缩20H,H为电源层与地层之间的距离。湖北什么是PCB设计报价信赖的 PCB 设计,赢得客户信赖。

如图一所说的R应尽量靠近运算放大器缩短高阻抗线路。因运算放大器输入端阻抗很高,易受干扰。输出端阻抗较低,不易受干扰。一条长线相当于一根接收天线,容易引入外界干扰。在图三的A中排版时,R1、R2要靠近三极管Q1放置,因Q1的输入阻抗很高,基极线路过长,易受干扰,则R1、R2不能远离Q1。在图三的B中排版时,C2要靠近D2,因为Q2三极管输入阻抗很高,如Q2至D2的线路太长,易受干扰,C2应移至D2附近。二、小信号走线尽量远离大电流走线,忌平行,D>=。三、小信号线处理:电路板布线尽量集中,减少布板面积提高抗干扰能力。四、一个电流回路走线尽可能减少包围面积。如:电流取样信号线和来自光耦的信号线五、光电耦合器件,易于干扰,应远离强电场、强磁场器件,如大电流走线、变压器、高电位脉动器件等。六、多个IC等供电,Vcc、地线注意。串联多点接地,相互干扰。七、噪声要求1、尽量缩小由高频脉冲电流所包围的面积,如下(图一、图二)一般的布板方式2、滤波电容尽量贴近开关管或整流二极管如上图二,C1尽量靠近Q1,C3靠近D1等。3、脉冲电流流过的区域远离输入、输出端子,使噪声源和输入、输出口分离。图三:MOS管、变压器离入口太近。

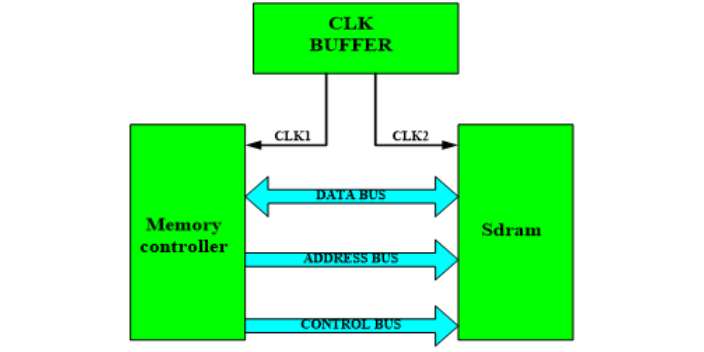

VTT电源孤岛尽可能靠近内存颗粒以及终端调节模块放置,由于很难在电源平面中单独为VTT电源划出一个完整的电源平面,因此一般的VTT电源都在PCB的信号层通过大面积铺铜划出一个电源孤岛作为vtt电源平面。VTT电源需要靠近产生该电源的终端调节模块以及消耗电流的DDR颗粒放置,通过减少走线的长度一方面避免因走线导致的电压跌落,另一方面避免各种噪声以及干扰信号通过走线耦合入电源。终端调节模块的sense引脚走线需要从vtt电源孤岛的中间引出。PCB设计是一门融合了艺术与科学的学问。

而直角、锐角在高频电路中会影响电气性能。5、电源线根据线路电流的大小,尽量加粗电源线宽度,减少环路阻抗,同时使电源线,地线的走向和数据传递方向一致,缩小包围面积,有助于增强抗噪声能力。A:散热器接地多数也采用单点接地,提高噪声抑制能力如下图:更改前:多点接地形成磁场回路,EMI测试不合格。更改后:单点接地无磁场回路,EMI测试OK。7、滤波电容走线A:噪音、纹波经过滤波电容被完全滤掉。B:当纹波电流太大时,多个电容并联,纹波电流经过个电容当纹波电流太大时,多个电容并联,纹波电流经过个电容产生的热量也比第二个、第三个多,很容易损坏,走线时,尽量让纹波电流均分给每个电容,走线如下图A、B如空间许可,也可用图B方式走线8、高压高频电解电容的引脚有一个铆钉,如下图所示,它应与顶层走线铜箔保持距离,并要符合安规。9、弱信号走线,不要在电感、电流环等器件下走线。电流取样线在批量生产时发生磁芯与线路铜箔相碰,造成故障。10、金属膜电阻下不能走高压线、低压线尽量走在电阻中间,电阻如果破皮容易和下面铜线短路。11、加锡A:功率线铜箔较窄处加锡。B:RC吸收回路,不但电流较大需加锡,而且利于散热。C:热元件下加锡,用于散热。 专业 PCB 设计,保障电路高效。黄冈什么是PCB设计销售

量身定制 PCB,满足个性化需求。黄冈什么是PCB设计销售

接收在预先配置的布局检查选项配置窗口上输入的检查选项和pinsize参数;将smdpin中心点作为基准,根据输入的所述pinsize参数,以smdpin的半径+预设参数阈值为半径,绘制packagegeometry/pastemask层面;获取绘制得到的所述packagegeometry/pastemask层面上所有smdpin的坐标,从而实现对遗漏的smdpin器件的pastemask的查找,减少layout重工时间,提高pcb布线工程师效率。附图说明为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍。在所有附图中,类似的元件或部分一般由类似的附图标记标识。附图中,各元件或部分并不一定按照实际的比例绘制。图1是本发明提供的pcb设计中layout的检查方法的实现流程图;图2是本发明提供的布局检查选项配置窗口的示意图;图3是本发明提供的接收在预先配置的布局检查选项配置窗口上输入的检查选项和pinsize参数的实现流程图;图4是本发明提供的将smdpin中心点作为基准,根据输入的所述pinsize参数,以smdpin的半径+预设参数阈值为半径,绘制packagegeometry/pastemask层面的实现流程图;图5是本发明提供的pcb设计中layout的检查系统的结构框图。 黄冈什么是PCB设计销售

仿真预分析:使用SI/PI仿真工具(如HyperLynx)验证信号反射、串扰及电源纹波。示例:DDR4时钟信号需通过眼图仿真确保时序裕量≥20%。3. PCB布局:从功能分区到热设计模块化布局原则:数字-模拟隔离:将MCU、FPGA等数字电路与ADC、传感器等模拟电路分区,间距≥3mm。电源模块集中化:将DC-DC转换器、LDO等电源器件放置于板边,便于散热与EMI屏蔽。热设计优化:对功率器件(如MOSFET、功率电感)采用铜箔散热层,热敏元件(如电解电容)远离发热源。示例:在LED驱动板中,将驱动IC与LED阵列通过热通孔(Via-in-Pad)连接至底层铜箔,热阻降低40%。信号流向: 尽...

- 恩施了解PCB设计 2025-11-26

- 黄冈设计PCB设计厂家 2025-11-26

- 恩施定制PCB设计规范 2025-11-26

- 鄂州打造PCB设计怎么样 2025-11-26

- 咸宁设计PCB设计销售电话 2025-11-26

- 武汉哪里的PCB设计功能 2025-11-26

- 恩施专业PCB设计教程 2025-11-26

- 哪里的PCB设计布线 2025-11-21

- 荆州常规PCB设计原理 2025-11-21

- 襄阳高速PCB设计哪家好 2025-11-21

- 黄石正规PCB设计功能 2025-11-21

- 鄂州高速PCB设计 2025-11-13

- 宜昌什么是PCB设计包括哪些 2025-11-13

- 咸宁专业PCB设计报价 2025-11-13

- 武汉高效PCB设计厂家 2025-11-13

- 宜昌常规PCB设计 2025-11-13

- 荆州印制PCB制板厂家 12-06

- 咸宁印制PCB制板多少钱 12-06

- 湖北打造PCB制板布线 12-06

- 湖北生产PCB制板厂家 12-06

- 宜昌印制PCB制板功能 12-06

- 孝感了解PCB制板包括哪些 12-06

- 武汉高速PCB制板原理 12-06

- 孝感高速PCB制板哪家好 12-05

- 孝感高速PCB制版加工 12-05

- 随州PCB制板厂家 12-05