一个简单的PLL频率综合器表现出各种限制和权衡。对频率综合器性能的主要影响是由为了实现较高的频率所需的大分频比和较高的分辨率引起的。注意由PLL器件产生的任何噪声以20logN的速度恶化,其中N为分频比。工作在小步长的传统的整数分频锁相环,分频比较大是因为步长必须等于鉴相器的比较频率。结果相位噪声大幅恶化。此外频率综合器的切换速度由其环路带宽决定,因此受限于鉴相器比较频率。由于环路滤波器带外抑制不足,或者甚至环路不稳定,增加环路带宽可能会导致更高频的参考杂散。因此,这个简单的单环架构锁相环受限于相互排斥的设计目标。它通常用于要求不高的应用领域或侧重于低成本应用。频率综合器在无线电、通信和计算机领域中使用。可应用于调制解调、时钟生成和数字信号处理等方面。北京频率综合器低相位噪声本振

VCO的频率受到误差信号的影响,产生输出信号。输出信号经过除频器进行频率分频,并与参考信号进行相位比较,修正误差信号。通过不断调节VCO的频率,使得输出信号的相位差逐渐减小,**终与参考信号同步。通过反馈回路,将修正后的误差信号重新送入相频比较器,不断进行比较和修正,直到输出信号与输入信号的频率完全同步。通过不断的相位比较、误差修正和频率调整的过程,锁相环能够实现输入信号与输出信号的频率同步,并将输出信号稳定在输入信号的频率上。简单易操作频率综合器市场报价频率综合器有什么用?

频率综合器的工作原理分别是:直接模拟合成法、锁相环合成法和直接数字合成法。直接模拟合成法利用倍频、分频、混频及滤波,从单一或几个参数频率中产生多个所需的频率。该方法频率转换时间快(小于100ns),但是体积大、功耗大,已基本不被采用。锁相环合成法通过锁相环完成频率的加、减、乘、除运算。该方法结构简化、便于集成,且频谱纯度高,使用比较广,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。

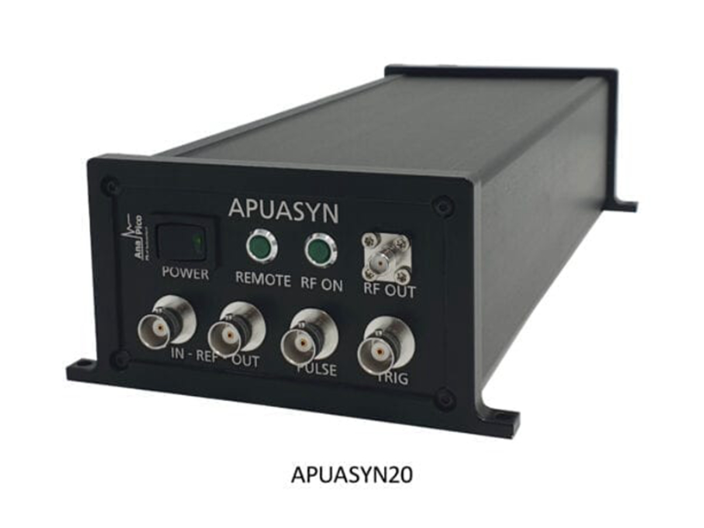

一种降低小数分频杂散的聪明的做法是利用一个可变参考频率。该技术基于一个小数N分频综合器的杂散的位置是其特定分频比和输出频率的函数的原理。因此,对于一个给定的输出频率,可以通过改变参考频率和相应的分频比的方式来移动(然后过滤掉)一个不想要的杂散。这涉及到频率规划,因此需要一个额外的频率综合器(用作参考频率)。此外尽管减小了分频比,其依然可能大到影响PLL性能。Anapico始终秉承瑞士制造的精神,坚持为用户提供精密的产品,主要产品包括射频微波信号源、相位噪声分析仪、频率综合器等,并在量子物理,5G通信、雷达和卫星等射频微波领域为用户提供测试测量解决方案。 频率综合器可以实现非常高的频率精度。

与传统概念相反,直接数字频率综合器利用数字信号处理技术根据参考时钟频率一点一点地在时域上构造一个输出信号波形。刚开始,使用相位累加器和查表来创建所需信号的数字代码。然后使用一个数字到模拟转换器(DAC)来重新构造一个正弦波或其它所需波形。使用低通滤波器滤除杂散,完成波形创建。这个过程非常快速,主要受数字控制逻辑的速度限制。因此频率切换速度非常高,和直接模拟方案速度差不多。DDS还具有相当低的相位噪声,甚至能改善(受其残留本底噪声限制)其时钟源本身的相位噪声。然而有价值的DDS的特性是其由相位累加器的长度确定的极精细的频率分辨率,很容易实现亚赫兹的水平。AnaPico频率综合器快至5μs的捷变频模块。福建相参频率综合器哪家好

频率综合器非常适合需要高性能和低抖动的应用,例如高速数据通信和精密测量。北京频率综合器低相位噪声本振

频率合成器的基本工作过程的VCO频率的稳定过程:当VCO处于正常工作状态时,输出一个固定的频率。若某种外界因素如电压、温度导[插图]致频率升高,则分频输出的信号为,比基准信号f1高,鉴相器检测到这个变化后,输出电压减小,使变容二极管两端的反偏电压减小。这使得变容二极管的结电容增大,振荡回路改变,输出频率降低。若外界因素导致频率下降,整个控制环路则执行相反的过程。VCO频率的变频过程:上面说明的是怎样使VCO电路输出的频率稳定。那怎样使VCO电路的频率能改变呢?一般来说,f2与f1具有如下关系:f2=Nf1,显而易见,只要改变预置分频器的预置数N,就可以改变输出频率f2值,实现多种频率的合成。北京频率综合器低相位噪声本振