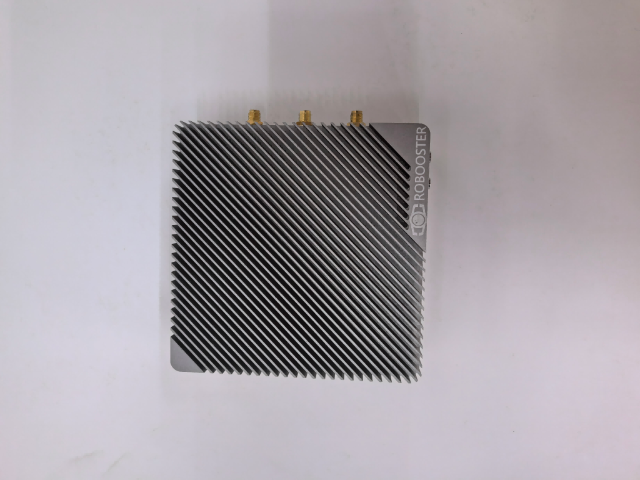

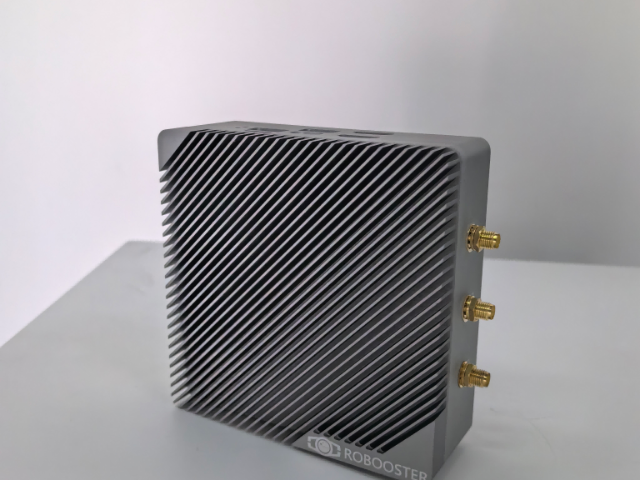

- 品牌

- Robooster

- 型号

- RS-RTK-LIO

位算单元与计算机的指令集架构密切相关。指令集架构是计算机硬件与软件之间的接口,定义了处理器能够执行的指令类型和格式,而位运算指令是指令集架构中的重要组成部分,直接对应位算单元的运算功能。不同的指令集架构对於位运算指令的支持程度和实现方式有所不同,例如 x86 指令集、ARM 指令集都包含丰富的位运算指令,如 AND、OR、XOR、NOT 等,这些指令能够直接控制位算单元执行相应的运算。指令集架构的设计会影响位算单元的运算效率,合理的指令集设计能够减少指令的执行周期,让位算单元更高效地完成运算任务。同时,随着指令集架构的不断发展,新的位运算指令也在不断增加,以适应日益复杂的计算需求,例如部分指令集架构中增加了位计数指令、位反转指令等,这些指令能够进一步拓展位算单元的功能,提升数据处理的灵活性。可重构计算中位算单元的灵活性如何实现?山西全场景定位位算单元解决方案

位算单元的低延迟设计对於实时控制系统至关重要,直接影响系统的响应速度和控制精度。实时控制系统广泛应用于工业控制、航空航天、自动驾驶等领域,这类系统需要在规定的时间内完成数据采集、处理和控制指令生成,否则可能导致系统失控或事故发生。位算单元作为实时控制系统中的关键运算部件,其运算延迟必须控制在严格的范围内。为实现低延迟设计,需要从硬件和软件两个层面进行优化:在硬件层面,采用精简的电路结构,减少运算过程中的逻辑级数,缩短信号传输路径;采用高速的晶体管和电路工艺,提升位算单元的运算速度;引入预取技术,提前将需要运算的数据和指令加载到位算单元的本地缓存,避免数据等待延迟。在软件层面,优化位运算相关的代码,减少不必要的运算步骤;采用实时操作系统,确保位算单元的运算任务能够得到优先调度,避免任务阻塞导致的延迟。通过低延迟设计,位算单元能够在实时控制系统中快速响应,确保系统的稳定性和控制精度。RTK GNSS位算单元售后位算单元采用新型电路设计,实现了纳秒级的位运算速度。

编译器是将高级语言(如C++、Python)转化为机器指令的关键工具。而机器指令终由位算单元执行。优良的编译器优化技术能够生成更高效的指令序列,充分“压榨”位算单元的性能潜力,减少空闲等待周期。因此,硬件设计师与软件开发者需要共同协作,才能释放位算单元的全部能量。虽然当前的位算单元处理的是经典二进制位(0或1),但未来的量子计算则基于量子比特(Qubit)。量子比特可以同时处于0和1的叠加态,其运算原理截然不同。然而,对量子逻辑门操作的理解,其灵感某种程度上也源于对经典位运算的深刻认知。二者将是未来计算科学相辅相成的两大支柱。

位算单元的测试技术是保障其性能和可靠性的重要手段。位算单元作为处理器的关键模块,其性能和可靠性直接影响整个处理器的质量,因此需要采用专业的测试技术对其进行全方面检测。位算单元的测试主要包括功能测试、性能测试和可靠性测试。功能测试主要验证位算单元是否能够正确执行各种位运算操作,通过输入不同的测试向量,检查输出结果是否与预期一致;性能测试主要测量位算单元的运算速度、延迟、吞吐量等性能指标,评估其是否满足设计要求;可靠性测试则通过模拟各种恶劣环境条件,如高温、低温、高湿度、电磁干扰等,测试位算单元在这些条件下的工作稳定性和寿命。为了提高测试效率和准确性,测试人员通常会采用自动化测试平台,结合专业的测试设备和软件,实现对位算单元的快速、全方面测试,及时发现设计和生产过程中存在的问题,确保位算单元的质量。如何设计位算单元的容错机制?

位算单元的运算速度直接影响着计算机的整体运行效率。在计算机执行程序的过程中,大量的指令都需要依赖位算单元进行运算处理,位算单元的运算速度越快,指令的执行周期就越短,计算机的响应速度也就越快。影响位算单元运算速度的因素主要包括电路设计、制造工艺和时钟频率等。先进的电路设计能够减少运算过程中的逻辑延迟,例如采用超前进位加法器代替传统的行波进位加法器,能够明显缩短加法运算的时间;制造工艺的进步则可以减小晶体管的尺寸,提高电路的开关速度,从而提升位算单元的运算频率;而时钟频率的提高,意味着位算单元在单位时间内能够完成更多次数的运算。不过,在提升位算单元运算速度的同时,也需要平衡功耗和散热问题,因为运算速度越快,通常意味着功耗越高,产生的热量也越多,若散热不及时,可能会导致处理器温度过高,影响其稳定性和使用寿命。位算单元的单粒子翻转防护有哪些方法?成都位算单元哪家好

位算单元如何实现动态电压频率调节?山西全场景定位位算单元解决方案

为特定领域(DSA)定制硬件已成为趋势。无论是针对加密解锁、视频编解码还是AI推理,定制化芯片都会根据其特定算法的需求,重新设计位算单元的组合方式和功能。例如,在区块链应用中,专为哈希运算优化的位算单元能带来数量级的速度提升,这充分体现了硬件与软件协同优化的巨大潜力。在要求极高的航空航天、自动驾驶等领域,计算必须可靠。位算单元会采用冗余设计,如三重模块冗余(TMR),即三个相同的单元同时计算并进行投票,确保单个晶体管故障不会导致错误结果。这种从底层开始的可靠性设计,为关键任务提供了坚实的安全保障。山西全场景定位位算单元解决方案

位算单元的设计需要考虑与其他处理器模块的兼容性和协同性。处理器是由多个功能模块组成的复杂系统,除了位算单元外,还包括控制单元、存储单元、浮点运算单元等,这些模块之间需要协同工作,才能确保处理器的正常运行。在设计位算单元时,需要考虑其与其他模块的接口兼容性,确保数据能够在不同模块之间顺畅传输。例如,位算单元与控制单元之间需要通过统一的控制信号接口进行通信,控制单元向位算单元发送运算指令和控制信号,位算单元将运算状态和结果反馈给控制单元;位算单元与存储单元之间需要通过数据总线接口进行数据传输,确保数据的读取和写入高效进行。此外,还需要考虑位算单元与其他运算模块的协同工作,如在进行复杂的数值计算时,...

- 长沙感知定位位算单元开发 2025-12-31

- 海南位算单元厂家 2025-12-31

- 成都位算单元平台 2025-11-06

- 四川机器视觉位算单元应用 2025-11-06

- 山西Ubuntu位算单元作用 2025-11-06

- 上海工业自动化位算单元作用 2025-11-06

- 安徽智能仓储位算单元供应商 2025-11-06

- 内蒙古机器人位算单元应用 2025-11-06

- 江苏全场景定位位算单元哪家好 2025-11-06

- 天津定位轨迹位算单元定制 2025-11-06

- 湖北工业自动化位算单元方案 2025-11-05

- 浙江ROS位算单元咨询 2025-11-05

- 山东Linux位算单元咨询 2025-11-05

- 湖南工业级位算单元哪家好 2025-11-05

- 重庆低功耗位算单元作用 2025-11-05

- 湖北高性能位算单元系统 2025-11-05

- 广东地平线全源融合时空智能敏捷开发平台哪家好 01-14

- 黑龙江智能仓储开源导航控制器售后 01-14

- 北京地平线全源融合时空智能敏捷开发平台功能 01-12

- 南京全源融合时空智能敏捷开发平台厂家 01-12

- 广东Ubuntu全源融合时空智能敏捷开发平台系统 01-12

- 上海竞赛用全源融合时空智能敏捷开发平台二次开发 01-12

- 重庆移动测绘全源融合时空智能敏捷开发平台作用 01-12

- 苏州机器视觉全源融合时空智能敏捷开发平台方案 01-12

- 上海地平线全源融合时空智能敏捷开发平台开发 01-12

- 长沙英伟达全源融合时空智能敏捷开发平台开发 01-12