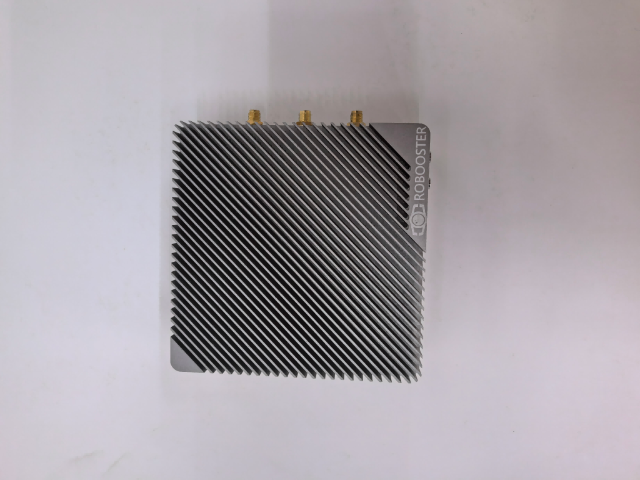

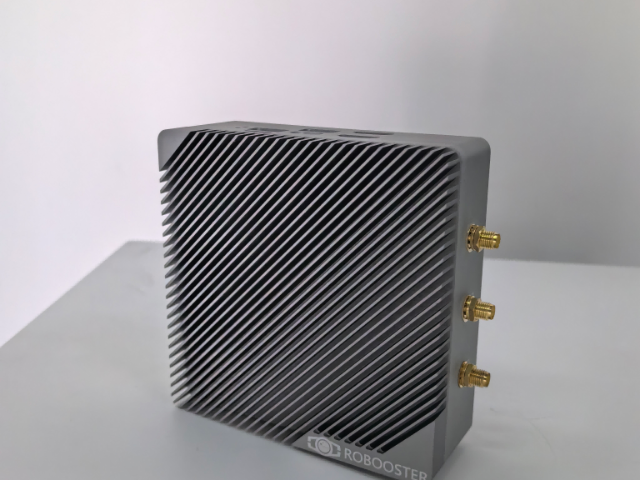

- 品牌

- Robooster

- 型号

- RS-RTK-LIO

位算单元的故障容错技术是提高处理器可靠性的重要保障。在一些对可靠性要求极高的领域,如航空航天、医疗设备、工业控制等,即使位算单元出现轻微故障,也可能导致严重的后果,因此需要采用故障容错技术,确保位算单元在出现故障时仍能正常工作或极小化故障影响。位算单元常用的故障容错技术包括冗余设计、错误检测与纠正(EDC/ECC)技术等。冗余设计是指在处理器中设置多个相同的位算单元,当主位算单元出现故障时,备用位算单元能够立即接替工作,保证运算的连续性;错误检测与纠正技术则是通过在数据中添加冗余校验位,位算单元在运算过程中对数据进行校验,检测出数据传输或运算过程中出现的错误,并通过校验位进行纠正。例如,在采用 ECC 内存的系统中,位算单元在处理内存中的数据时,能够通过 ECC 校验技术检测并纠正单比特错误,避免错误数据影响运算结果。这些故障容错技术的应用,大幅提高了位算单元的可靠性,满足了高可靠性领域的应用需求。位算单元的综合约束如何优化?合肥高性能位算单元解决方案

位算单元的低延迟设计对於实时控制系统至关重要,直接影响系统的响应速度和控制精度。实时控制系统广泛应用于工业控制、航空航天、自动驾驶等领域,这类系统需要在规定的时间内完成数据采集、处理和控制指令生成,否则可能导致系统失控或事故发生。位算单元作为实时控制系统中的关键运算部件,其运算延迟必须控制在严格的范围内。为实现低延迟设计,需要从硬件和软件两个层面进行优化:在硬件层面,采用精简的电路结构,减少运算过程中的逻辑级数,缩短信号传输路径;采用高速的晶体管和电路工艺,提升位算单元的运算速度;引入预取技术,提前将需要运算的数据和指令加载到位算单元的本地缓存,避免数据等待延迟。在软件层面,优化位运算相关的代码,减少不必要的运算步骤;采用实时操作系统,确保位算单元的运算任务能够得到优先调度,避免任务阻塞导致的延迟。通过低延迟设计,位算单元能够在实时控制系统中快速响应,确保系统的稳定性和控制精度。湖北智能仓储位算单元解决方案在金融计算中,位算单元加速了高频交易决策。

位算单元与计算机的指令集架构密切相关。指令集架构是计算机硬件与软件之间的接口,定义了处理器能够执行的指令类型和格式,而位运算指令是指令集架构中的重要组成部分,直接对应位算单元的运算功能。不同的指令集架构对於位运算指令的支持程度和实现方式有所不同,例如 x86 指令集、ARM 指令集都包含丰富的位运算指令,如 AND、OR、XOR、NOT 等,这些指令能够直接控制位算单元执行相应的运算。指令集架构的设计会影响位算单元的运算效率,合理的指令集设计能够减少指令的执行周期,让位算单元更高效地完成运算任务。同时,随着指令集架构的不断发展,新的位运算指令也在不断增加,以适应日益复杂的计算需求,例如部分指令集架构中增加了位计数指令、位反转指令等,这些指令能够进一步拓展位算单元的功能,提升数据处理的灵活性。

位算单元的并行处理能力对於提升大规模数据处理效率具有重要意义。随着大数据技术的发展,需要处理的数据量呈指数级增长,传统的串行运算方式已经无法满足数据处理的实时性需求,位算单元的并行处理能力成为关键。位算单元的并行处理能力主要体现在能够同时对多组二进制数据进行运算,通过增加运算单元的数量或采用并行架构设计,实现多任务的同步处理。例如,在大数据分析中的数据筛选和排序操作中,位算单元可以同时对多组数据进行位运算比较,快速筛选出符合条件的数据并完成排序,大幅缩短数据处理时间;在分布式计算中,多个节点的位算单元可以同时处理不同的数据块,通过协同工作完成大规模的数据运算任务。为了进一步提升并行处理能力,现代位算单元还会采用向量处理技术、SIMD(单指令多数据)架构等,能够在一条指令的控制下,同时对多个数据元素进行运算,进一步提高数据处理的吞吐量。量子位算单元与传统位算单元有何本质区别?

位算单元与操作系统之间存在着密切的交互关系。操作系统作为管理计算机硬件和软件资源的系统软件,需要根据应用程序的需求,合理调度处理器的资源,其中就包括对位算单元的使用调度。当应用程序需要进行位运算操作时,会通过操作系统向处理器发出指令请求,操作系统会将该请求转换为对应的机器指令,并分配处理器资源,让位算单元执行相应的位运算。在多任务操作系统中,多个应用程序可能同时需要使用位算单元,操作系统需要采用合理的调度算法,如时间片轮转调度、优先级调度等,协调不同任务对位算单元的使用,避免资源冲击,确保每个任务都能得到及时的运算支持。此外,操作系统还会通过驱动程序与位算单元进行交互,对其进行初始化和配置,确保位算单元能够正常工作,并向应用程序提供统一的接口,方便应用程序调用位算单元的功能。新型位算单元支持动态电压调节,功耗降低25%。天津智能仓储位算单元定制

可重构计算中位算单元的灵活性如何实现?合肥高性能位算单元解决方案

物联网(IoT)终端设备通常搭载各种传感器,持续产生原始数据。这些数据往往需要经过初步过滤、压缩或特征提取后再上传云端。内置在微控制器(MCU)中的位算单元可以高效地完成这些预处理任务,极大减少了需要传输的数据量,节省了通信带宽和设备功耗。在计算机体系结构和数字逻辑课程中,从门电路开始构建一个完整的位算单元是关键教学内容。通过FPGA等可编程硬件平台,学生可以亲手实现并验证其设计,深刻理解数据在计算机中底层的流动和处理方式,为未来从事芯片设计或底层软件开发打下坚实基础。合肥高性能位算单元解决方案

位算单元的设计需要考虑与其他处理器模块的兼容性和协同性。处理器是由多个功能模块组成的复杂系统,除了位算单元外,还包括控制单元、存储单元、浮点运算单元等,这些模块之间需要协同工作,才能确保处理器的正常运行。在设计位算单元时,需要考虑其与其他模块的接口兼容性,确保数据能够在不同模块之间顺畅传输。例如,位算单元与控制单元之间需要通过统一的控制信号接口进行通信,控制单元向位算单元发送运算指令和控制信号,位算单元将运算状态和结果反馈给控制单元;位算单元与存储单元之间需要通过数据总线接口进行数据传输,确保数据的读取和写入高效进行。此外,还需要考虑位算单元与其他运算模块的协同工作,如在进行复杂的数值计算时,...

- 长沙感知定位位算单元开发 2025-12-31

- 海南位算单元厂家 2025-12-31

- 成都位算单元平台 2025-11-06

- 四川机器视觉位算单元应用 2025-11-06

- 山西Ubuntu位算单元作用 2025-11-06

- 上海工业自动化位算单元作用 2025-11-06

- 安徽智能仓储位算单元供应商 2025-11-06

- 内蒙古机器人位算单元应用 2025-11-06

- 江苏全场景定位位算单元哪家好 2025-11-06

- 天津定位轨迹位算单元定制 2025-11-06

- 湖北工业自动化位算单元方案 2025-11-05

- 浙江ROS位算单元咨询 2025-11-05

- 山东Linux位算单元咨询 2025-11-05

- 湖南工业级位算单元哪家好 2025-11-05

- 重庆低功耗位算单元作用 2025-11-05

- 湖北高性能位算单元系统 2025-11-05

- 广东地平线全源融合时空智能敏捷开发平台哪家好 01-14

- 黑龙江智能仓储开源导航控制器售后 01-14

- 北京地平线全源融合时空智能敏捷开发平台功能 01-12

- 南京全源融合时空智能敏捷开发平台厂家 01-12

- 广东Ubuntu全源融合时空智能敏捷开发平台系统 01-12

- 上海竞赛用全源融合时空智能敏捷开发平台二次开发 01-12

- 重庆移动测绘全源融合时空智能敏捷开发平台作用 01-12

- 苏州机器视觉全源融合时空智能敏捷开发平台方案 01-12

- 上海地平线全源融合时空智能敏捷开发平台开发 01-12

- 长沙英伟达全源融合时空智能敏捷开发平台开发 01-12