- 品牌

- 士兰微,上海贝岭,新洁能,必易微

- 型号

- 10

- 制式

- 圆插头,扁插头

MOSFET(金属-氧化物-半导体场效应晶体管)是一种基于电场效应控制电流的半导体器件,其主要点结构由源极(S)、漏极(D)、栅极(G)及衬底(B)四部分组成,栅极与沟道之间通过一层极薄的氧化层(通常为SiO₂)隔离,形成电容结构。这种绝缘栅设计使得栅极电流极小(近乎零),输入阻抗极高,这是其区别于BJT(双极结型晶体管)的关键特性。在N沟道增强型MOSFET中,当栅极施加正向电压且超过阈值电压Vth时,氧化层下的P型衬底表面会形成反型层(N型沟道),此时源漏之间施加正向电压即可产生漏极电流Id;而P沟道类型则需施加负向栅压,形成P型沟道。这种电压控制电流的机制,使其在低功耗、高频应用场景中具备天然优势,成为现代电子电路的主要点器件之一。贝岭 BL 系列 MOSFET 适配工业控制场景,兼具高耐压与强电流承载能力。江苏mos级

LED驱动电路是一种用于控制和驱动LED灯的电路,它由多个组成部分组成。LED驱动电路的主要功能是将输入电源的电压和电流转换为适合LED工作的电压和电流,并保证LED的正常工作。LED驱动电路通常由以下几个组成部分组成:电源、电流限制电路、电压调节电路和保护电路。它提供了驱动电路所需的电源电压。常见的电源有直流电源和交流电源,根据实际需求选择合适的电源。电源的电压和电流需要根据LED的工作要求来确定,一般情况下,LED的额定电压和电流会在产品的规格书中给出。什么是MOS瑞阳微自研 RS2300 系列 MOSFET 采用 SOT23 封装,体积小巧且功耗较低。

MOS 的重心结构由四部分构成:栅极(G)、源极(S)、漏极(D)与半导体衬底(Sub),整体呈层状堆叠设计。栅极通常由金属或多晶硅制成,通过一层极薄的氧化物绝缘层(传统为二氧化硅,厚度只纳米级)与衬底隔离,这也是 “绝缘栅” 的重心特征;源极和漏极是高浓度掺杂的半导体区域(N 型或 P 型),对称分布在栅极两侧,与衬底形成 PN 结;衬底为低掺杂半导体材料(硅基为主),是载流子(电子或空穴)运动的基础通道。根据衬底掺杂类型与沟道导电载流子差异,MOS 分为 N 沟道(电子导电)和 P 沟道(空穴导电)两类;按导通机制又可分为增强型(零栅压时无沟道,需加正向电压开启)和耗尽型(零栅压时已有沟道,加反向电压关断)。关键结构设计如绝缘层厚度、栅极面积、源漏间距,直接影响阈值电压、导通电阻与开关速度等重心性能。

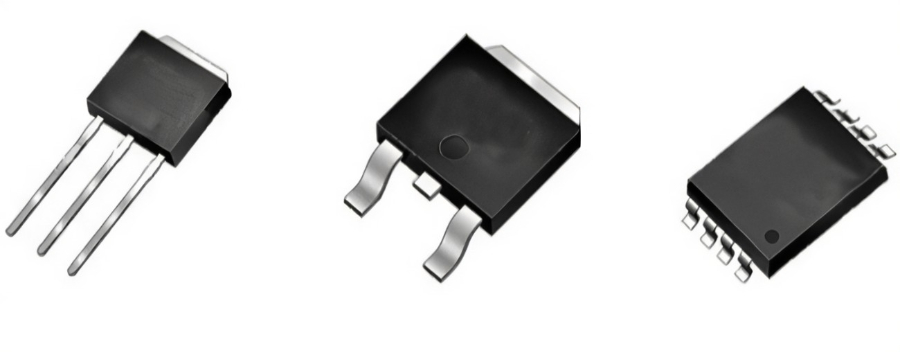

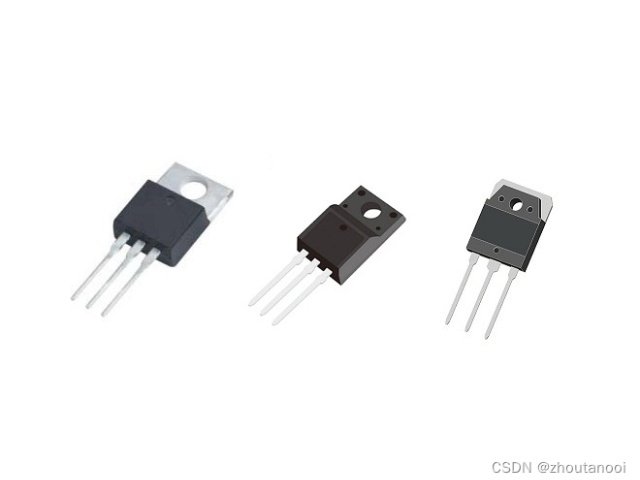

热管理是MOSFET长期稳定工作的关键,尤其在功率应用中,散热效率直接决定器件寿命与系统可靠性。MOSFET的散热路径为“结区(Tj)→外壳(Tc)→散热片(Ts)→环境(Ta)”,每个环节的热阻需尽可能降低。首先,器件选型时,优先选择TO-220、TO-247等带金属外壳的封装,其外壳热阻Rjc(结到壳)远低于SOP、DIP等塑料封装;对于高密度电路,可选择裸露焊盘封装(如DFN、QFN),通过PCB铜皮直接散热,减少热阻。其次,散热片设计需匹配功耗:根据器件的较大功耗Pmax和允许的结温Tj(max),计算所需散热片热阻Rsa(散热片到环境),确保Tj=Ta+Pmax×(Rjc+Rcs+Rsa)≤Tj(max)(Rcs为壳到散热片的热阻,可通过导热硅脂降低)。此外,强制风冷(如风扇)或液冷可进一步降低Rsa,适用于高功耗场景(如电动车逆变器);PCB布局时,MOSFET应远离发热元件,预留足够散热空间,且铜皮面积需满足电流与散热需求,避免局部过热。士兰微 SVF4N60F MOSFET 性价比出众,广受小家电厂商青睐。

接下来是电流限制电路,它用于限制LED的工作电流,以保证LED的正常工作。LED是一种电流驱动的器件,过大的电流会导致LED热量过大,缩短其寿命,甚至损坏LED。因此,电流限制电路的设计非常重要。常见的电流限制电路有电阻限流电路、电流源电路和恒流驱动电路等。电压调节电路是为了保证LED的工作电压稳定。LED的工作电压与其颜色有关,不同颜色的LED具有不同的工作电压范围。电压调节电路可以通过稳压二极管、稳压芯片等方式来实现,以保证LED在不同工作条件下都能正常工作。它用于保护LED免受过电流、过电压等不良因素的损害。保护电路可以通过添加保险丝、过压保护芯片等方式来实现。瑞阳微 MOSFET 品质有保障,赢得众多长期合作客户的认可与信赖。使用MOS批发价格

瑞阳微提供全系列 MOSFET 选型服务,满足不同客户个性化技术要求。江苏mos级

MOSFET的动态特性测试聚焦于开关过程中的参数变化,直接关系到高频应用中的开关损耗与电磁兼容性(EMC)。动态特性测试主要包括上升时间tr、下降时间tf、开通延迟td(on)与关断延迟td(off)的测量,需使用示波器与脉冲发生器搭建测试电路:脉冲发生器提供栅极驱动信号,示波器同步测量Vgs、Vds与Id的波形。

上升时间tr是指Id从10%上升到90%的时间,下降时间tf是Id从90%下降到10%的时间,二者之和决定了开关速度(通常为几十至几百纳秒),速度越慢,开关损耗越大。开通延迟是指从驱动信号上升到10%到Id上升到10%的时间,关断延迟是驱动信号下降到90%到Id下降到90%的时间,延迟过大会影响电路的时序控制。此外,动态测试还需评估米勒平台(Vds下降过程中的平台期)的长度,米勒平台越长,栅极电荷Qg越大,驱动损耗越高。在高频应用中,需选择tr、tf小且Qg低的MOSFET,减少动态损耗。 江苏mos级

MOS 的应用可靠性需通过器件选型、电路设计与防护措施多维度保障,避免因设计不当导致器件损坏或性能失效。首先是静电防护(ESD),MOS 栅极绝缘层极薄(只几纳米),静电电压超过几十伏即可击穿,因此在电路设计中需增加 ESD 防护二极管、RC 吸收电路,焊接与存储过程中需采用防静电包装、接地操作;其次是驱动电路匹配,栅极电荷(Qg)与驱动电压需适配,驱动电阻过大易导致开关损耗增加,过小则可能引发振荡,需根据器件参数优化驱动电路;第三是热管理设计,大电流应用中 MOS 的导通损耗与开关损耗会转化为热量,结温过高会加速器件老化,需通过散热片、散热膏、PCB 铜皮优化等方式提升散热效率,确保结温控制...

- 使用MOS 2026-03-23

- IGBTMOS收费 2026-03-22

- 高科技MOS如何收费 2026-03-22

- 什么是MOS销售方法 2026-03-22

- 使用MOS代理品牌 2026-03-22

- 威力MOS现价 2026-03-21

- 标准MOS一体化 2026-03-21

- 哪里有MOS使用方法 2026-03-20

- 应用MOS什么价格 2026-03-20

- 威力MOS使用方法 2026-03-20

- 定制MOS成本价 2026-03-18

- 高科技MOS厂家现货 2026-03-18

- 哪些是MOS供应 2026-03-18

- 常规MOS销售厂 2026-03-17

- 国产MOS价格对比 2026-03-17

- 大规模MOS销售方法 2026-03-17

- 哪里有IGBT批发价格 04-04

- 大规模IGBT厂家供应 04-04

- IGBT价格比较 04-04

- 什么是IGBT价格对比 04-04

- 大规模IGBT哪里买 04-03

- 国产IGBT使用方法 04-03

- 出口IGBT销售厂 04-03

- 高科技IGBT商家 04-03

- 现代化IGBT收费 04-03

- 新能源IGBT平均价格 04-02