芯片封装的人才培养:芯片封装行业的发展离不开专业人才的支撑。中清航科注重人才培养,建立了完善的人才培养体系,通过内部培训、外部合作、项目实践等方式,培养了一批既懂技术又懂管理的复合型人才。公司还与高校、科研机构合作,设立奖学金、共建实验室,吸引优秀人才加入,为行业源源不断地输送新鲜血液,也为公司的持续发展提供人才保障。芯片封装的未来技术展望:未来,芯片封装技术将朝着更高度的集成化、更先进的异构集成、更智能的散热管理等方向发展。Chiplet技术有望成为主流,通过将不同功能的芯粒集成封装,实现芯片性能的跨越式提升。中清航科已提前布局这些前沿技术的研发,加大对Chiplet互连技术、先进散热材料等的研究投入,力争在未来技术竞争中占据带头地位,为客户提供更具前瞻性的封装解决方案。芯片封装良率影响成本,中清航科工艺改进,将良率提升至行业前列。江苏ic的气密性封装

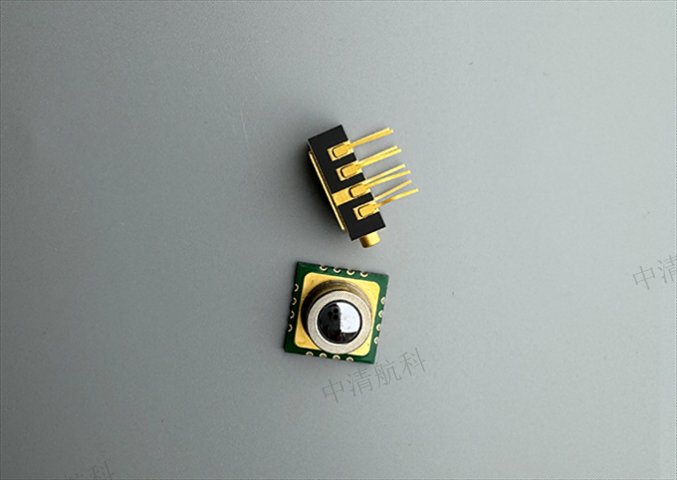

常见芯片封装类型-PGA:的PGA为插针网格式封装,芯片内外有多个方阵形插针,沿芯片四周间隔排列,可根据引脚数目围成2-5圈,安装时需插入专门的PGA插座。从486芯片开始,出现了ZIF(零插拔力)插座,方便PGA封装的CPU安装和拆卸。PGA封装插拔操作方便、可靠性高,能适应更高频率。中清航科在PGA封装方面拥有专业的技术与设备,可为计算机、服务器等领域的客户,提供适配不同频率要求的高质量PGA封装芯片。有相关需求欢迎随时联系我司。江苏smt元件封装0402中清航科聚焦芯片封装创新,用模块化设计满足多样化应用需求。

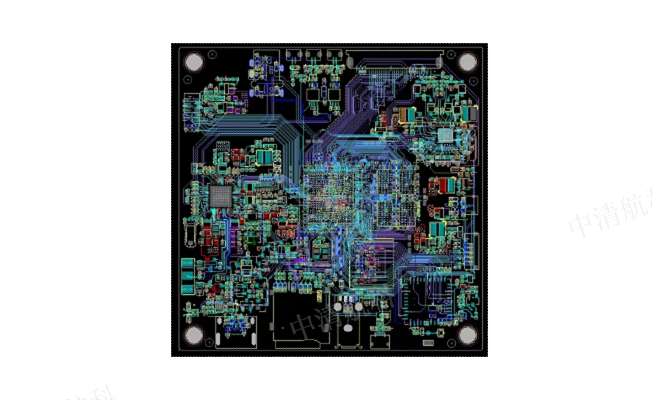

中清航科部署封装数字孪生系统,通过AI视觉检测实现微米级缺陷捕捉。在BGA植球工艺中,球径一致性控制±3μm,位置精度±5μm。智能校准系统使设备换线时间缩短至15分钟,产能利用率提升至90%。针对HBM内存堆叠需求,中清航科开发超薄芯片处理工艺。通过临时键合/解键合技术实现50μm超薄DRAM晶圆加工,4层堆叠厚度400μm。其TSV深宽比达10:1,阻抗控制在30mΩ以下,满足GDDR6X1TB/s带宽要求。中清航科可拉伸封装技术攻克可穿戴设备难题。采用蛇形铜导线与弹性体基底结合,使LED阵列在100%拉伸形变下保持导电功能。医疗级生物相容材料通过ISO10993认证,已用于动态心电图贴片量产。

针对车规级芯片AEC-Q100认证痛点,中清航科建成零缺陷封装产线。通过铜柱凸点替代锡球焊接,结合环氧模塑料(EMC)三重防护层,使QFN封装产品在-40℃~150℃温度循环中通过3000次测试。目前已有17家Tier1供应商采用其AEC-QGrade1封装解决方案。中清航科多芯片重构晶圆(ReconstitutedWafer)技术,将不同尺寸芯片集成于300mm载板。通过动态贴装算法优化芯片排布,材料利用率提升至92%,较传统WLCSP降低成本28%。该方案已应用于物联网传感器批量生产,单月产能达500万颗。功率芯片封装热密度高,中清航科液冷集成方案,突破散热效率瓶颈。

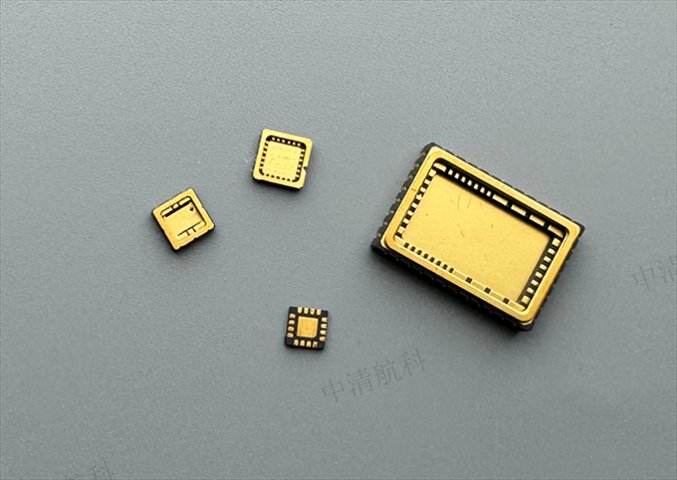

先进芯片封装技术-系统级封装(SiP):SiP是将多个不同功能的芯片以并排或叠加的方式,封装在一个单一的封装体内,实现系统级的功能集成。与SoC(系统级芯片)相比,SiP无需复杂的IP授权,设计更灵活、成本更低。中清航科在SiP技术上积累了丰富经验,能够根据客户需求,将多种芯片高效整合在一个封装内,为客户提供具有成本优势的系统级封装解决方案,广泛应用于消费电子、汽车电子等领域。想要了解更多详细内容可以关注我司官网。中清航科芯片封装工艺,通过自动化升级,提升一致性降低不良率。江苏smt元件封装0402

中清航科芯片封装技术,平衡电气性能与机械保护,延长芯片使用寿命。江苏ic的气密性封装

随着摩尔定律逼近物理极限,先进封装成为提升芯片性能的关键路径。中清航科在Fan-Out晶圆级封装(FOWLP)领域实现突破,通过重构晶圆级互连架构,使I/O密度提升40%,助力5G射频模块厚度缩减至0.3mm。其开发的激光解键合技术将良率稳定在99.2%以上,为毫米波通信设备提供可靠封装方案。面对异构集成需求激增,中清航科推出3DSiP立体封装平台。该方案采用TSV硅通孔技术与微凸点键合工艺,实现CPU、HBM内存及AI加速器的垂直堆叠。在数据中心GPU领域,其散热增强型封装结构使热阻降低35%,功率密度提升至8W/mm²,满足超算芯片的严苛要求。江苏ic的气密性封装