为应对Chiplet集成挑战,中清航科推出自主知识产权的混合键合(HybridBonding)平台。采用铜-铜直接键合工艺,凸点间距降至5μm,互连密度达10⁴/mm²。其测试芯片在16核处理器集成中实现8Tbps/mm带宽,功耗只为传统方案的1/3。中清航科研发的纳米银烧结胶材料突破高温封装瓶颈。在SiC功率模块封装中,烧结层导热系数达250W/mK,耐受温度600℃,使模块寿命延长5倍。该材料已通过ISO26262认证,成为新能源汽车OBC充电模组优先选择方案。中清航科深耕芯片封装,以可靠性设计,助力芯片在极端环境工作。江苏dfn封装测试

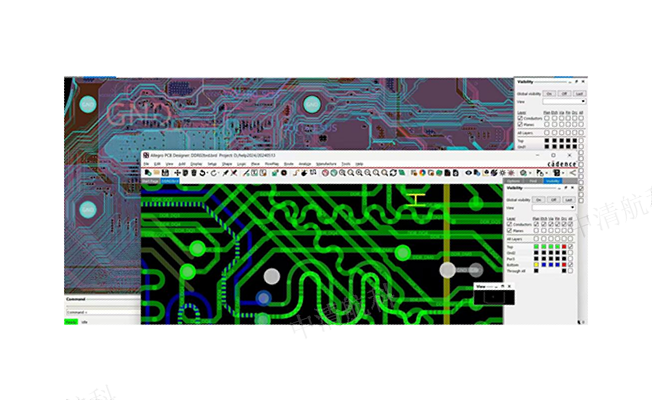

面向CPO共封装光学,中清航科开发硅光芯片耦合平台。通过亚微米级主动对准系统,光纤-光栅耦合效率>85%,误码率<1E-12。单引擎集成8通道112GPAM4,功耗降低45%。中清航科微流控生物芯片封装通过ISO13485认证。采用PDMS-玻璃键合技术,实现5μm微通道密封。在PCR检测芯片中,温控精度±0.1℃,扩增效率提升20%。针对GaN器件高频特性,中清航科开发低寄生参数QFN封装。通过金线键合优化将电感降至0.2nH,支持120V/100A器件在6GHz频段工作。电源模块开关损耗减少30%。江苏tsv封装技术中清航科芯片封装工艺,通过仿真优化,提前规避量产中的潜在问题。

随着摩尔定律逼近物理极限,先进封装成为提升芯片性能的关键路径。中清航科在Fan-Out晶圆级封装(FOWLP)领域实现突破,通过重构晶圆级互连架构,使I/O密度提升40%,助力5G射频模块厚度缩减至0.3mm。其开发的激光解键合技术将良率稳定在99.2%以上,为毫米波通信设备提供可靠封装方案。面对异构集成需求激增,中清航科推出3DSiP立体封装平台。该方案采用TSV硅通孔技术与微凸点键合工艺,实现CPU、HBM内存及AI加速器的垂直堆叠。在数据中心GPU领域,其散热增强型封装结构使热阻降低35%,功率密度提升至8W/mm²,满足超算芯片的严苛要求。

针对TMR传感器灵敏度,中清航科开发磁屏蔽封装。坡莫合金屏蔽罩使外部场干扰<0.1mT,分辨率达50nT。电流传感器精度达±0.5%,用于新能源汽车BMS系统。中清航科微型热电发生器实现15%转换效率。Bi₂Te₃薄膜与铜柱互联结构使输出功率密度达3mW/cm²(ΔT=50℃)。物联网设备实现供能。中清航科FeRAM封装解决数据保持难题。锆钛酸铅薄膜与耐高温电极使10¹²次读写后数据保持率>99%。125℃环境下数据保存超10年,适用于工业控制存储。中清航科聚焦芯片封装,用环保材料替代,响应绿色制造发展趋势。

芯片封装的散热设计:随着芯片集成度不断提高,功耗随之增加,散热问题愈发突出。良好的散热设计能确保芯片在正常温度范围内运行,避免因过热导致性能下降甚至损坏。中清航科在芯片封装过程中,高度重视散热设计,通过优化封装结构、选用高导热材料、增加散热鳍片等方式,有效提升封装产品的散热性能。针对高功耗芯片,公司还会采用先进的液冷散热封装技术,为客户解决散热难题,保障芯片长期稳定运行,尤其在数据中心、高性能计算等领域发挥重要作用。芯片封装需精密工艺,中清航科以创新技术提升散热与稳定性,筑牢芯片性能基石。江苏tsv封装技术

中清航科聚焦芯片封装,用仿真预判风险,缩短研发验证周期。江苏dfn封装测试

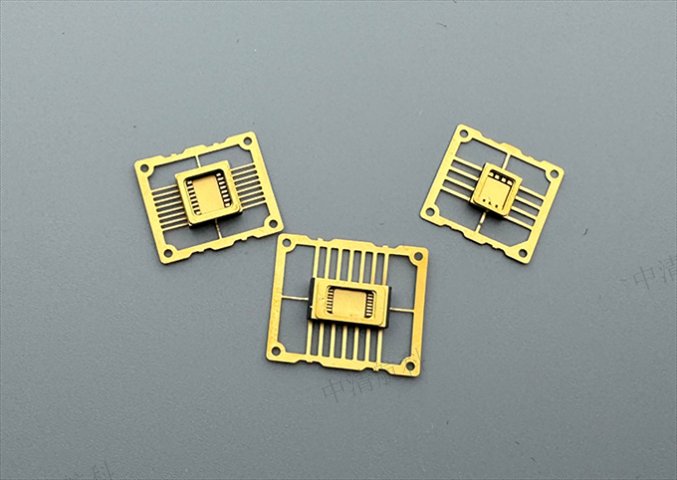

先进芯片封装技术-系统级封装(SiP):SiP是将多个不同功能的芯片以并排或叠加的方式,封装在一个单一的封装体内,实现系统级的功能集成。与SoC(系统级芯片)相比,SiP无需复杂的IP授权,设计更灵活、成本更低。中清航科在SiP技术上积累了丰富经验,能够根据客户需求,将多种芯片高效整合在一个封装内,为客户提供具有成本优势的系统级封装解决方案,广泛应用于消费电子、汽车电子等领域。想要了解更多详细内容可以关注我司官网。江苏dfn封装测试